PCIe如何紧随计算和网络步伐?

judy 在 周二, 04/30/2024 - 10:23 提交

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

高速差分PCI-Express 总线的应用场景越来越广阔,为了提高总线上数据传输的效率

本文提供有关 Versal™ ACAP 集成块 for PCI Express® 内核的详细信息,IP 性能和资源利用率数据。

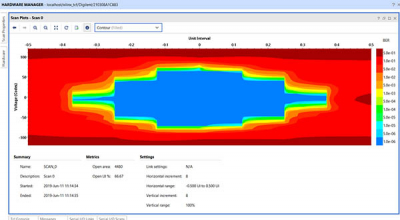

In-system IBERT 可提供 PCIe 链接眼图。“JTAG Debugger”和“In-system IBERT”功能结合在一起即可提供即时信息,用于判断链接训练问题的可能原因。在本篇博文中,我们将讲解如何使用这些功能。本篇博文基于赛灵思 VCU118 开发板随附的 UltraScale+ 器件。

PCIe 链路训练及稳定性问题形成了绝大多数互联互通问题。

本文档主要介绍在带集成工具的 Xilinx Vivado 设计套件中调试这些问题的使用案例。

本文档将重点介绍如何通过捕获在 UltraScale FPGA Gen3 集成块中用于 PCI Express 内核的链路训练调试信号来使用 Vivado ILA 进行调试。