作者:潘金龙,李德建,王于波,冯曦,董长征,冯文楠,来源:计算机技术与应用

高速差分PCI-Express 总线的应用场景越来越广阔,为了提高总线上数据传输的效率,从 PCI-Express 的总线结构、带宽开销点、系统参数配置进行说明,并通过对不同长度的报文在读、写传输的背景下进行理论分析与计算,得到了提升总线传输效率的合理配置,实现了 PCI-Express 总线传输效率的显著提升。

随着现代处理器技术的飞速 发展使用高速差分总线替代并行总线的应用场景越来越多。与单端信号相比.高速差分信号可以使用更高的时钟频率,使用更少的信号线,完成之前需要很多单端并行数据信号才能达到的总线带宽。如何高效地利用总线带宽,通过何种配置达到最优应用,给设计者带来了挑战。

1. 总线概述

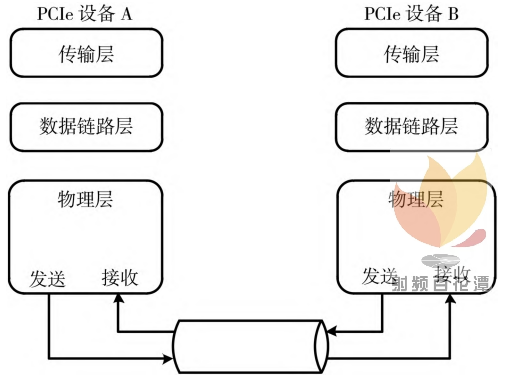

PCI-Express(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,简称 PCIe。PCIe属于高速串行点对点双通道高带 宽传输,互联设备之间独立传输,主要有主动电源管理、错误报告 端对端的可靠性传输、热插拔以及服务质量等功能。PCIe 是一种分层协议,由传输层、数据链路层和物理层组成,层级结构如图 1所示。PCIe A 设备与 B 设备之间通过发送端与接收端进行互联。

图 1 PCIe 层级结构图

2. 传输效率影响因素分析

数据在 PCIe 总线各层级传输所产生的开销主要在以下几个方面

2.1 数据编码开销

数据编码开销主要是 PCIe 的物理层产生的,GEN(generation)1/2 使用 8b/10b 编码GEN3/4/5 使用 128b/130b 编码,编码的目的是保持直流平衡(DC balance)。

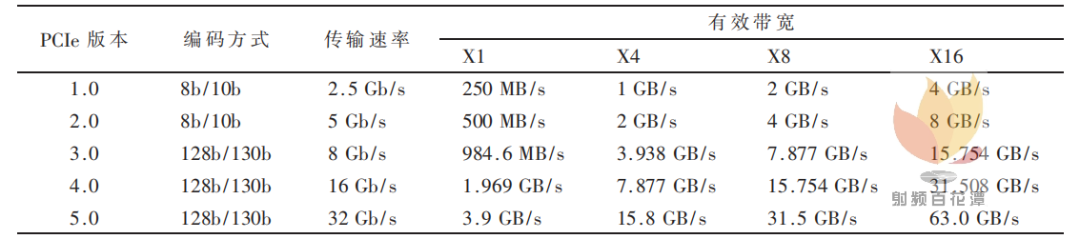

PCIe 各版本传输速率如表 1 所示(Xn 表示存在 n 条物理链路,例如 X4 表示存在 4 条物理链路)。

表1 PCIe 传输速率

例如 PCIe 1.0 使用 8b/10b 编码方案,导致占用了20%(2/10)的原始信道带宽。那么 PCIe 1.0 实际上单通道的有效带宽就是 2.5 Gb/sx80%/8=250 MB/s。

2.2 TLP(Transaction Layer Packet)开销

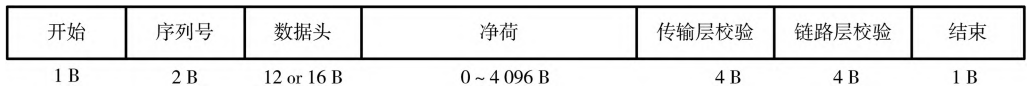

PCIe 报文为分层封装协议的报文。数 据 报 文 在Device A 产生之后,在事务层(Transaction Layer) 报文由数 据头(Header)、报文净荷(Payload)、端到端的 CRC(ECRC)组成,经过数据链路层(Data Link Layer)后增加序列号(Sequence Number)、链路层 CRC(LCRC)、开始(Start)结束(End)数据块,然后通过物理层(Physical Layer)发出。PCIe Gen1/2 报文格式如图 2 所示,PCIe Gen3/4/5/报文格式如图 3 所示。

图 2 PCIe Gen1/2 报文格式

图 3 PCIe Gen3/4/5 报文格式

PCIe Gen3/4/5 的报文结构开始(Start)标识是4B且没有结束(End)标识,这是与 Gn1/2 报文结构上的区别。

在 TLP 传输过程中,相关的报文标识就增加了 20~30B的开销。

2.3 控制报文开销

控制报文来自于数据链路层,报文长度为 6 B,主要功能是保证来自事务层的 TLP 在 PCIe 链路中正确传递。报文的类型主要有应答 Ack (Acknowledge)、非 应答Nak(No acknowledge)、功耗管理 PM(Power Manage)、流控FC(Flow Control) 等。

2.3.1 Ack 与 Nak 报文开销

发送端发出 TLP 报文之后,需要接收端回应 Ack 或者 Nak 报文,来确认发送的 TLP 是否被成功接收。发送端在发送 TLP 的同时需要将 TLP 复制一份保存在 TLPretry buffer(TLP 重传缓存)中,直到收到 Ack 即表示成功接收的回应。如果收到了 Nak 则表示未成功接收的回应,需要将存储在 TLP retry buffer 中的 TLP 再次发送,直到被正确接收。Ack 不需要与 TLP 一一对应,可以设置一个计数器 N,发送 N 个 TLP 之后,接收端回应个 Ack。接收端会对报文进行错误检查(Error Check),如果查询到接收的报文序号不正确或有其他的错误,则回应一个 Nak,发送端将会重新发送 TLP。数据传输结构如图 4 所示。

2.3.2 PM 报文开销

PCIe 设备进入 LO 状态 (PCI 设备的正常工作状态后,物理层为了解决接收时钟与本地时钟之间漂移所带来的频差问题,每一个链路(Lane)需要在传输1180~1538个字符后发送一个 SKP(PCIe 链路层传输的一种报文)请求来进行时钟补偿,在 TLP 的传输过程中不会插入时钟补偿。

2.3.3 流量控制报文开销

流量控制的主要作用是在发送端和接收端进行 数据传递时,通过 FC 报文传递本端存储空间的使用状态避免因为接收端缓冲区由于存储空间不足导致丢弃来自发送端的数据。如果 FC 报文没有及时发送,会导致本地存储空间不够而丢弃报 文,反之 FC 报文发送太过频繁,就会导致 PCIe 传输的性能下降带宽利用率低。

2.4 系统参数对传输效率的影响

系统配置参数如下:

有效负载最大值:MPS(Maximum Payload Size)。PCIe设备所传送所有类型报文的数据大小不能超过 MPS。MPS 支持的大小有 6 种 :128B 、256B、 512B、1024B、2048 B、4096B。当 PCIe 设备所传送的数据大小超过MPS 参数时数据将被分割为多个 TLP 进行发送了。

最大读请求数据;MRRS(Maximum Read Request Szie).PCIe 设备一次能从目标设备读取的最大数据,如果一次存储器读操作需要读取的数据范围大于 MRRS 时,该PCIe 设备需要向目标设备发送多个存储器读操作MRRS 的大小同样有6种:128B、256B、512B、1 024B、2048B 、4096B。

RCB(Read Completion Boundary):RCB可配置为64B或者128B,RCB 的大小与完成报文的有效负载相关在 PCIe 总线中,一个存储器读请求 TLP 可能收到目标设备发出的多个读完成报文后,才能完成一次存储器读操作。

3. 传输效率计算

报文在 PCIe 总线传输过程中,实际的有效带宽和物理带宽之间的关系是如何呈现的?下面以存储器写请求TLP 和存储器读请求 TLP 传输为例来分析 PCI 总线的性能。

3.1 存储器写请求 TLP

(1)应用场景

DPCIe 物理层为 Gen2,2Lane ;

发送的报文数目Num 为 200 个,每个报文的长度和 MPS 相同;

MPS 设置为 1024B;

Ack 功能配置为传输 10 个 TLP 报文回复1个 Ack ;

FC 功能配置为传输 5 个报文回复 1个 FC ;

传输层数据的报文头为 4DW.再加上其他开销共计28B。

(2)带宽计算

需要传递的报文总长度:200x1 024=204 800 B

实际传递的报文总长度

不含有 PM 报文开销的长度 :(1 024+28)x200+(6+2)x200/10+(6+2)x200/20=210 640 B。

PM 报文开销,定义1200 bit 插入 1个PM 报文210 640x8/1 200=1 404 个,注意在 TLP 每个报文发送过程中不能插入 PM 报文,所以在 TLP 发送间隔时会插入多个 PM 报文。

总传递报文长度为:210 640+1 404x(6+2)=221 872 B

C. 有效带宽

需要传递的报文总长度/总传递报文长度=204 800/221 872=92.31%

PCIe Gen2 的物理有效带宽为80%,所以最终2个Lane 的传输性能为:92.31%x0.8=73.84%,带宽为 5 Gb/sx2x73.84%=7.384 Gb/s,即 10 Gb/s 的物理传输通道有效带宽为 7.384 Gb/s。

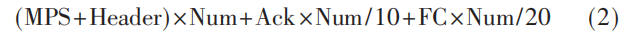

(3)导出公式

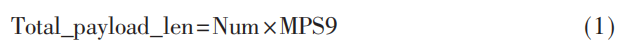

根据以上计算结果,可以推到出如下公式

a. 需要传递的报文总长度

b. 实际传递的报文总长度

不含有 PM 报文开销的长度:

PM 报文开销,定义 1 200 bit 插入 1个 PM 报文。

总传递报文长度为 :

c. 有效带宽

(4)延伸拓展

报文在总线传输过程中,配置都是固化好的,通过对有效带宽的计算公式可以看出在报文实际传输的过程中,报文的有效数据长度和 MPS 参数越接近越好,这样可以减少传输的次数。另外 MPS 参数的值越大,有效带宽就越高。将 MPS 参数设置为 128 B、256 B、512 B、1 024 B、2 048 B、4 096 B、TLP 报文的有效数据长度同MPS 参数.存储器写请求 TLP 的不同 MPS 配置的带宽效率结果如表 2 所示。

表2 不同 MPS 配置带宽效率表

从计算结果来看,随着 MPS 的增大带宽有效利用率在提高,但是增加幅度在变小。

(5)其他说明

在上面第 4 点中对带宽的利用率做了表格的描述但是实际上还应该算上 PCIe Gen2 物理带宽 8b/10b 解码的开销,即实际的带宽效率还应在上面计算的基础上乘以 0.8 才是最终的带宽效率。

3.2 存储器读请求 TLP

(1)应用场景

a. PCIe 物理层为 Gen2,2Lane ;

b. 发送的报文数目 Num 为 200 个;

c. MRRS 设置为 1 024 B ;

d. Ack 功能配置为传输 10 个 TLP 报文回复 1个 Ack ;

e.FC 功能配置为传输 5个报文回复 1个 FC ;

f. 传输层数据的报文头为 4DW.再加上其他开销共计 28 B;

g. RCB 设置为 64 B。

(2)带宽计算

a. 需要传递的报文总长度:200x1 024=204 800 B。

b. 实际传递的报文总长度

每个存储器读请求 TLP 需要传输 的次数 :MRRS/RCB=1 024 B/64 B=16,即需要返回 16 个 TLP 读完成报文才能将此次读的数据全部获取。

不含有PM 报文开销的长度 :(1 024+28x16)x200+(6+2)x200/10+(6+2)X200/20=294 640 B。

PM 报文开销,定义 1200 bit 插人 1个 PM 报文210 640x8/1 200=2 个,注意在 TLP 每个报文发送过程中不能插入 PM 报文,所以在 TLP 发送间隔时会插入多个 PM 报文。

总传递报文长度为:294 640+1 964x(6+2)=310 354 B

c.有效带宽

需要传递的报文总长度/总传递报文长度=204 800/310 354=65.99%。

PCIe Gen2的物理有效带宽为80%所以最终的2个Lane 的传输性能为 :65.99%x0.8=52.79%,带宽为 5 Gb/sx2x52.79%=5.279 Gb/s,即 10 Gb/s 的物理传输通道,有效带宽为 5.279 Gb/s。

(3)导出公式

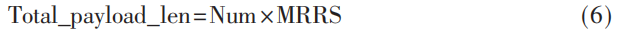

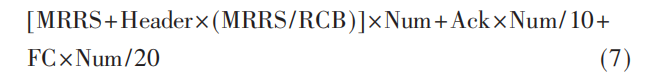

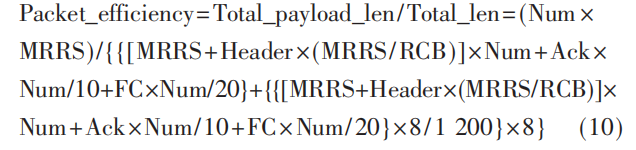

根据以上计算结果,可以推到出如下公式:

a. 需要传递的报文总长度

b. 实际传递的报文总长度

不含有 PM 报文开销的长度:

PM 报文开销,定义 1200 bit 插人 1个 PM 报文:

总传递报文长度为 :

c. 有效带宽

(4)延伸拓展

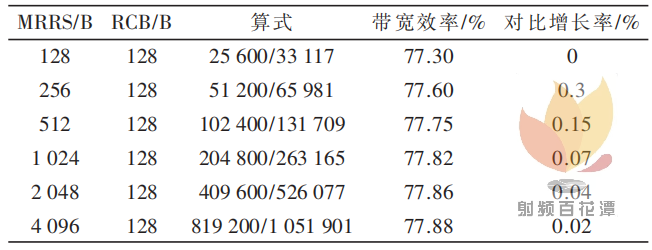

将 MRRS 参数设置为 128 B、256 B、512 B、1 024 B、2 048 B、4 096 B,存储器读请求 TLP 的不同 MRRS 带宽效率如表 3 所示。

表 3 不同 MRRS(RCB/64 B)配置带宽效率结果

从计算结果来看,随着 MRRS 的增大,带宽有效利用率并没有显著提高,基本上没有明显的变动。将 RCB的参数由 64 B 修改为 128 B 的结果如表 4 所示。

表 4 不同 MRRS(RCB/128 B)配置带宽效率结果

对 比表 3 和表 4相同的 MRRS 配置,RCB 的值由64 B 变成了 128 B,带宽有效利用率有了明显的提升。例如 MRRS 配置为 128 B,RCB 配置为 64 B,带宽有效率是65.62%:而当 RCB 配置为128 B,带宽有效率是 77.30%.带宽提升了 12.04%。

(5)其他说明

与存储器写请求 TLP 相同,存储器读请求 TLP 的实际带宽也需要考虑 PCIe Gen2 物理传输通道编解码的开销。

结论

本文介绍了 PCIe 总线的基本结构,列举了影响 PCIe总线传输效率的多种原因,从实际应用中进行举例说明并计算。当然上面存储器写请求与存储器读请求的带宽有效利用率的计算只是粗略的估算,报文在实际的发送与接收过程中会涉及软件、硬件的配合处理与其他多种原因的影响,实际应用中会比理论值要低一些。如何高效地应用 PCIe 总线,只有深入理解了总线传输的原理才能通过合理、有效的配置提高传输效率。

本文转载自:高速射频百花潭微信公众号