Serdes系列总结——Xilinx serdes IP使用(一):3G serdes

judy 在 周一, 08/08/2022 - 16:39 提交

一个线速率为3.072G的,输入为20bit,输出为20bit的无协议无编码的4对serdes例程,参考时钟为153.6MHz

一个线速率为3.072G的,输入为20bit,输出为20bit的无协议无编码的4对serdes例程,参考时钟为153.6MHz

长时间没有做高速相关的FPGA单板开发,一直停留在GTX和GTP的时代,是时候梳理一下,从Xilinx的7系列到目前的ultrascale系列

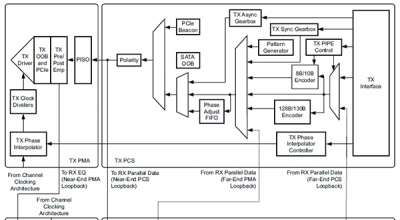

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

串行器/解串器(SerDes)电路多年来一直在帮助芯片间进行告诉数据通信,但新的工艺技术正迫使它以意想不到的方式进行调整和改变。

终于到了今天的猪脚-SerDes,为什么拿SGMII和SerDes进行对比,主要原因是,SerDes是一个串行接口,和SGMII很像,和GMII几乎没有什么交集,所以两者对比就没有什么实际意义,所以只进行SGMII和SerDes进行对比。