在Vitis中通过 PSU DDR 执行MicroBlaze应用

judy 在 周五, 05/12/2023 - 08:20 提交

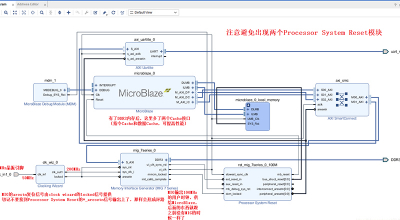

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

MicroBlaze 软核嵌入式处理器是高度可定制的 IP 核,支持 70 多个配置选项

本节介绍最简单的实验工程,用串口打印helloworld。

本文介绍了当MicroBlaze包含在DFX可重构模块(RM)内时,更新MicroBlaze Block RAM的内容。

Xilinx FPGA MicroBlaze使用AXI 1G/2.5G Ethernet Subsystem(= Tri Mode Ethernet MAC + AXI Ethernet Buffer)以太网IP核驱动RTL8211FD千兆网口,并使用lwip2.1.2协议栈建立http服务器,支持IPv6

MicroBlaze™处理器参考指南提供了有关32位和64位软处理器MicroBlaze的信息,它是Vivado®设计套件的一部分。该文件旨在作为MicroBlaze硬件架构的指南。

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。

该演示视频将为您展示如何使用处理器预设设计创建 MicroBlaze 处理器系统。

在Vitis里面创建了一个LwIP工程,调试的时候发现,在BRAM里面运行正常,但如果改到DDR3内存里面运行,启动时就会卡死在sleep函数上。于是建立了一个Hello World工程来检查,代码如下:

本教程以米联客XC7A35T FGG484-2开发板为例,详细讲解一下用Xilinx Vivado 2020.1创建MicroBlaze软核工程,然后再用Xilinx Vitis 2020.1建立Hello World C程序工程的完整操作步骤。