【工程师分享】MicroBlaze大内部存储器(AXI BRAM)设计

judy 在 周四, 06/17/2021 - 09:54 提交

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

本文介绍如何将低功率域 (LPD) 作为一个通道和 PL 中的一个三模冗余 MicroBlaze 来创建和实现单片通用 2 通道系统。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。在ZCU106单板上,有312个Block RAM,有96个Ultra RAM。客户需要1MB存储空间。

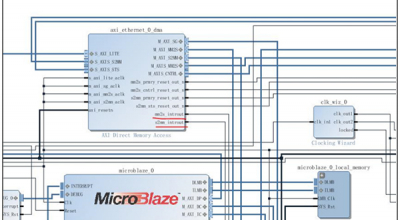

在ZC702单板上,MicroBlaze通过IC/DC端口连接到PS S_AXI_GP0,MicroBlaze读取OCM,得到值DECODE1C。MicroBlaze改为通过DP端口连接到PS S_AXI_GP0,再读取OCM,正常。

lwip 是瑞典计算机科学院(SICS)的 Adam Dunkels 开发的一个小型开源的 TCP/IP 协议栈。实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用。LwIP 是 Light Weight (轻型)IP 协议,有无操作系统的支持都可以运行。LwIP 实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用,它只需十几 KB 的 RAM 和 40K 左右的 ROM 就可以运行

亲眼目睹在 Xilinx 器件中构建一款功能强大的定制处理系统有多轻松。了解 Xilinx MicroBlaze 处理器预设,其可使全新设计的跨越式启动变得更轻松!Vivado 的 IP 集成器工具库和第三方 IP 库无需 RTL 经验。您将了解到如何使用外设在仅仅几分钟内对几乎任何嵌入式设计进行快速原型设计

本次视频重点介绍了赛灵思嵌入式软件工具 2018.3 版本的新功能,以及基础架构的重要更新。内容涉及包括 PetaLinux 增强功能,Linux 和 U-Boot 更新以及 MicroBlaze 更新等等。

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型

在本次研讨会中,赛灵思专家将向您介绍赛灵思MicroBlaze 处理器将如何让启动新设计变得前所未有地简单快捷!无需 RTL 经验就能使用 Vivado IP 集成器工具以及第三方 IP 库。专家将为您演示如何使用外围设备在几分钟之内快速打造任何嵌入式设计原型