All node

RAM的应用

judy 在 周四, 07/28/2022 - 10:19 提交

本文主要从工程角度出发,阐述RAM在工程中的实际问题。

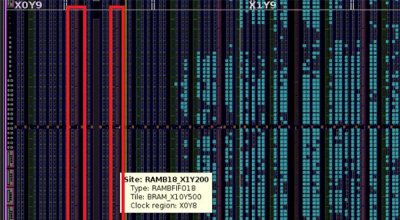

Vivado的DFX(Dynamic Function eXchange)功能

judy 在 周四, 07/28/2022 - 09:16 提交

DFX功能实际上就是部分可重配置功能,开启可重配置功能时,FPGA内部的逻辑可以分割为两种不同类型

Xilinx 7系列SelectIO结构之IO属性和约束

judy 在 周三, 07/27/2022 - 15:49 提交

通过属性或者约束可以访问7系列FPGA I/O资源某些特性。本文我们介绍和I/O资源相关的属性和约束

基于Xilinx的时序分析与约束(1)——什么是时序分析?什么是时序约束?什么又是时序收敛?

judy 在 周三, 07/27/2022 - 11:51 提交

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

FPGA Base 循环、条件生成语句

judy 在 周三, 07/27/2022 - 10:41 提交

在FPGA编码的时候,如果多使用生成块语句,敲代码的时间大大减少。但是,代码的可读性会更高。

(更新)什么样的电脑配置跑Vivado FPGA综合最快?

judy 在 周三, 07/27/2022 - 10:38 提交

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)

TCL语法中的array命令

judy 在 周二, 07/26/2022 - 18:29 提交

array命令:可以查询一个数组变量中已经定义的元素的信息。

Enclustra FPGA核心板在声纳系统中的应用

judy 在 周二, 07/26/2022 - 11:15 提交

本文讨论的声纳发射器是一个相控阵发射器,能够发射10Khz至100Khz的频率。该系统采用了一个发射器模块阵列,每个模块能够驱动8个声纳传感器。

Virtex® UltraScale+™ HBM 使用心得(3)——与DDR对比分析

judy 在 周二, 07/26/2022 - 09:31 提交

本文主要是和DDR的对比,对项目前期的选型做一分析。