本文转载自:孤独的单刀的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

写在前面

时序约束与分析是FGPA开发过程中一项必备的技能,同时也是设计开发中相对较难的部分。很多人一谈起FPGA开发,言必称时序约束,搞得好像不会时序分析就不会进行FPGA开发一样。

举个例子:我以前面试某公司的硬件工程师职位,2面面试官是嵌入式软件出身的技术经理,聊天过程中偶然提到了我会点儿FPGA,结果他只问了我会不会做时序约束,得到我肯定的答复后,一口认定我的FPGA水平很高(实际半吊子水)。这样的看法虽然不够准确,但也代表了许多工程师的心声----FPGA的时序约束仍是一门较高级的技能。

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

磨刀不误砍柴工

正所谓磨刀不误砍柴工,在学习时序内容之前,有一些相关的概念有必要先学一下。

(1)时钟 Clock

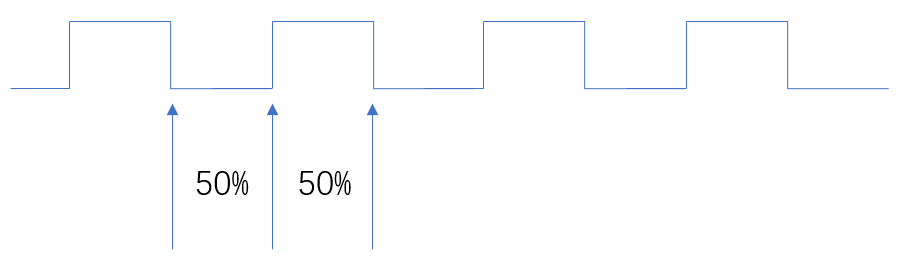

理想的时钟模型是一个占空比为 50%且周期固定的方波。时钟是 FPGA 中同步电路逻辑运行的一个基准。如下图所示:

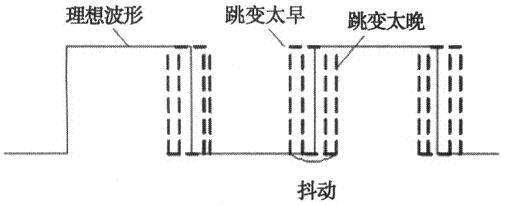

(2)时钟抖动 Clock Jitter

理想的时钟信号是完美的放波,但是实际的方波是存在一些时钟抖动的。那么什么是时钟抖动呢? 时钟抖动, Clock Jitter,是相对于理想时钟沿,实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动(时钟脉冲宽度发生暂时变化,也就是 T cycle【时钟周期】或大或小)。 如下图所示:

(3)时钟偏差 Clock Skew

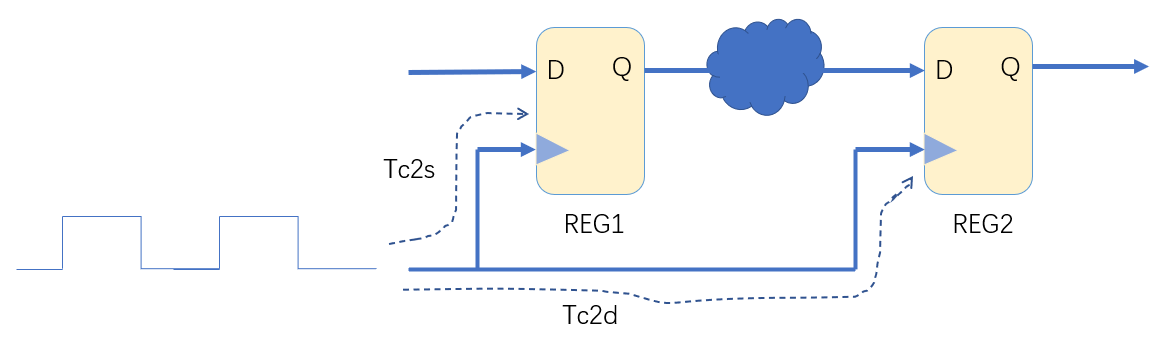

时钟偏差,Clock Skew,是指同一个时钟域内的时钟信号到达数字电路各寄存器所用时间的差异。 时序分析的起点一般是源寄存器(reg1),终点一般是目标寄存器(reg2)。时钟

信号也会走线,那么和其它信号的传输一样,就会有延时。下图中,时钟信号从时钟源传输到源寄存器的延时我们定义为 Tc2s,传输到目标寄存器的延时我们定义为 Tc2d。如下图所示:

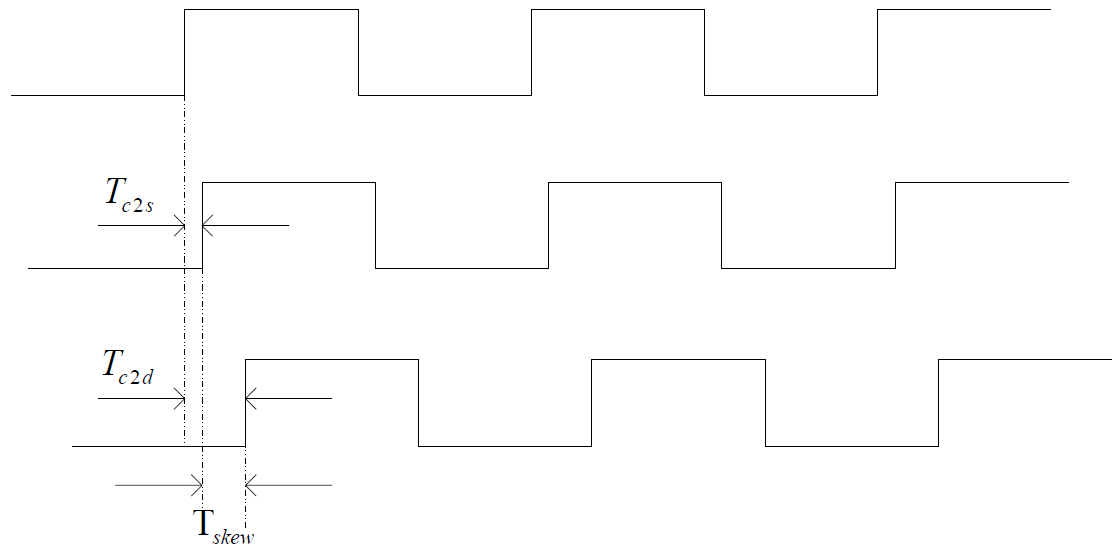

时钟网络延时 Tskew 就是 Tc2d 与 Tc2s 之差,即 Tskew=Tc2d-Tc2s。如下图所示:

第一个方波是时钟源,第二个方波为时钟到达 REG1 时的波形,第三个方波为时钟到达 REG2 时的波形,从图上可以看出 Tskew 是时钟到达两个寄存器时的相位偏差。

(4)时钟不确定性 Clock Uncertainty

Clock Uncertainty ,即时钟的不确定性。时钟的不确定性主要是由 Clock Skew 和 Jitter 构成。 因此 Clock Uncertainty = Clock Skew + Clock Jitter。大家搞明白什么是 Skew和 Jitter,那么也就明白什么是 Clock Uncertainty。

一般标准的时序约束文件中,都需要加 Clock Uncertainty 的约束,这个约束是为了让时序分析更贴近真实的电路设计。 对于 Uncertainty 的设置,每种工艺,或者每种设计来说,都不尽相同。

(5)同步电路和异步电路

简单来讲,FPGA 设计中寄存器全部使用一个时钟的设计是同步设计电路,FPGA 设计寄存器使用多个时钟的设计是异步设计电路。我们说的所有时序分析都是建立在同步电路的基础上的,异步电路不能做时序分析(或者说只能做伪路径约束)。

异步电路由于使用的时钟不同,导致上游寄存器的输出数据进入下游寄存器的时间是任意的,这非常可能导致不满足下游寄存器的建立时间要求和保持时间要求,从而导致亚稳态。同样的原因,由于两者时钟不同,所以也不法建立对应的模型来分析异步电路是否能满足时序要求。

(6)建立时间(Setup Time)和保持时间(Hold Time)

建立时间和保持时间是寄存器的固定属性,为了能够是寄存器稳定的采样到当前D端的数据,D端数据必须满足建立时间和保持时间的要求:

通俗来讲:建立时间和保持时间就是在寄存器采样窗口中输入数据必须保持不变,以免寄存器无法稳定采样。也就是说,在我寄存器的采样窗口之前你输入数据就必须要保持稳定,即输入数据不能来的太晚(建立时间);同样的,你寄存器的输入数据也必须在我寄存器的采样窗口结束后才变化,在此之前必须保持问题,即输入数据不能走的太早(保持时间)。

建立时间和保持时间的示意图如下:

建立时间和保持时间的概念非常重要,一定要记住。因为,我们所谓的时序分析(静态时序分析STA),简单来讲就是使用特定的模型来判断当前设计中的所有寄存器的建立时间和保持时间能否被满足。也就是说,时序分析,就是分析每个寄存器的建立时间和保持时间是不是符合要求的。

什么是时序分析?

时序分析主要有两种办法:

STA不需要输入向量就能穷尽所有的路径,运行速度快,占用内存小。不仅可以对芯片设计进行全面的时序功能检查,还可以利用时序分析的结果来优化设计。DTA的优点是结果精确,并且适用于更多的设计类型;缺点是速度慢,并且可能会遗漏一些关键路径。一般来讲,我们提到的时序分析都是指静态时序分析STA。

了解了上述概念后,我们就明白了,时序分析实际上就是分析设计中每个寄存器的建立时间和保持时间能否被满足。

什么是时序约束?

了解了时序分析后,其实时序约束也就好理解了。简单来讲,时序约束就是你要告诉综合工具,你的标准是什么。综合工具应该如何根据你的标准来布线,以满足所以寄存器的时序要求。

在FPGA设计中,一旦时钟频率上升,那么时钟周期就会减少。不难想象频率越高,时钟周期越小,而建立时间和保持时间的要求不变,那么对应的,满足建立时间和保持时间也会变难,因为留给信号到达的窗口变小了嘛!

但是综合工具怎么知道你的设计要求是多少?那它怎么去约束时钟呢?所以我们开发者都告诉综合工具,我们的约束标准是什么,综合工具才可以根据这个标准去布线,从而满足我们的时序要求。

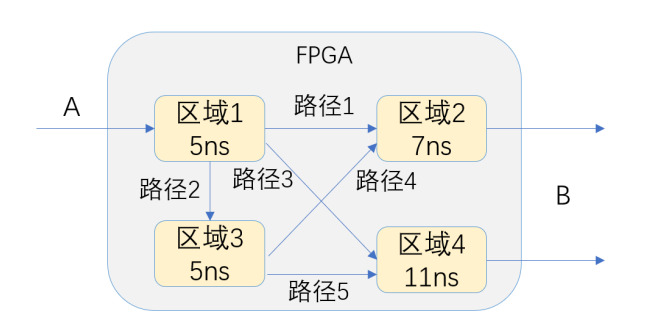

假设信号需要从输入到输出在 FPGA 内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在 FPGA 内部的延时不能超过 13ns(约束条件),而开发工具在执行过程中找到了下图所示的一些可能的布局布线方式。图中区域 1 的延迟是 5ns,区域 2 的延迟是 7ns,区域 3 的延迟是 5ns,区域 4 的延迟是 11ns。那么,怎样的布局布线能够达到我们的要求呢?仔细分析一番,发现所有路径的延时可能为 12ns(走路径 1)、16ns(走路径 3)、21ns(走路径 2 到路径 5)、17ns(走路径 2 到路径 4),只有 1 条路径能够满足要求,布局布线工具就会选择满足要求的路径 1。

这个地方我们系统要求这个信号在 FPGA 内部的延时不能超过 13ns,是有 1 条路径可以满足要求的,那么如果系统要求这个信号在 FPGA 内部的延时不能超过 5ns,那么没有任何一条路径可以满足要求,这个就说明这个 FPGA 器件速度等级比较慢,可以选择速度等级比较快的 FPGA 器件,当然也有可能是系统要求过于苛刻(过约束)。

如果系统要求这个信号在 FPGA 内部的延时不能超过 18ns,那么是有 3 条路径可以满足要求的,分别是走路径 1,走路径 3,走路径 2 到路径 4 这 3 条路径,这个说明如果系统要求松,那么布局布线工具可以选择就很多,这样对布局布线工具比较友好。 时序分析的前提就是我们先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。如果我们不添加时序约束,那么时序分析工具就不会去分析时序和做时序收敛。也就是说,只有在对设计添加了时序约束后,系统的时序问题才有可能暴露出来。

什么是时序收敛?

在我们给出时序约束的标准后,综合工具会自动进行时序分析,然后出具时序报告表。如果我们的设计欠佳或者约束条件过高,导致综合工具无法实现满足我们要求的布线,这种情况下,设计是不满足时序要求的。

通过修改设计(如减少扇出、重新布线优化、重定时、流水线切割等一系列方法)或其他方法,来使综合工具能重新实现满足我们设计要求的布线的这一设计过程,就被称为时序收敛Timing closure,同样的,当所有的时序设计要求被满足后,也可以说这一设计是时序收敛的。

简单点讲,时序收敛就是你改作业的过程,把不及格的作业通过改、抄等手段给改到合格的过程就是时序收敛。

好的时序是设计出来的,不是约束出来的 。好的约束必须以好的设计为前提。没有好的设计,在约束上下再大的功夫也是没有意义的。不过,通过正确的约束也可以检查设计的优劣,通过时序分析报告可以检查出设计上时序考虑不周的地方,从而加以修改。通过几次“ 分析—修改—分析” 的迭代也可以达到完善设计的目标。应该说,设计是约束的根本,约束是设计的保证,二者是相辅相成的关系。