UltraFast 设计方法时序收敛参考指南

judy 在 周三, 11/03/2021 - 10:06 提交

《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛:

《UltraFast 设计方法时序收敛快捷参考指南》提供了以下分步骤流程, 用于根据《UltraFast设计方法指南》( UG949 )中的建议快速完成时序收敛:

长期以来,EDA 面临着各种挑战:器件数量越来越多、设计越来越复杂。尽管摩尔定律逐步放缓,但在过去 20 多年间,FPGA 晶体管数量呈现的指数级增长丝毫未减。赛灵思利用堆叠硅片互联等技术,在异构集成方面取得了领先地位,同时还增加了 ARM 处理器子系统、AI 引擎或众多连接块

2021 年 4 月,赛灵思取得了令人激动的阶段性成果——宣布业界领先的 Versal™ AI Core 和 Versal Prime 系列器件实现全面量产和付运。如同我们的宇宙一样,Versal 生态系统也在持续迅速扩张,涵盖更加广泛

Kria KV260视觉AI入门套件是一个开箱即用平台,开发人员可以通过首选设计环境,在任何抽象层添加定制和差异化功能,包括应用软件、AI模型乃至FPGA设计。本文描述了Kria™ KV260 Vision AI启动套件。

Xilinx 建议将时序约束和物理约束分开保存为两个不同的文件。甚至可以将针对某一个模块的约束单独保存在一个文件中。可以使用 USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 属性指定约束文件是在综合或实现过程中使用。

本节教程介绍如何使用SDSoC软件创建硬件平台,并且使用它来加速程序函数。

本篇文章要写的是调试Xilinx网络IP时踩到的一个坑,也是控制PHY芯片时的一个坑,板卡上的PHY芯片是非常经典的88E1111,使用MDIO接口控制。

IEEE 1588 是一个精密时间协议 (PTP),用于同步计算机网络中的时钟。在局域网中,它能将时钟精确度控制在亚微秒范围内,使其适于测量和控制系统。IEEE 1588 标准为时钟分配定义了一个主从式架构,由一个或多个网段及一个或多个时钟组成。TSN 网络中时间同步协议使用 IEEE 802.1AS 协议,它基于IEEE 1588 协议进行精简和修改,也称为 gPTP 协议。

根据用户指南,要符合预配置 BSDL 文件描述要求,PUDC_B 应该设置为 1。在实际 BSDL 文件中,我只看到了 PROGRAM_B 的合规性:

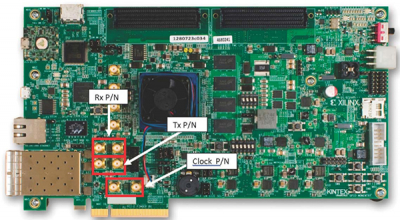

本文提供一个系统,旨在通过利用每个串行千兆位收发器内的功能来取代外部压控晶体振荡器(VCXO)电路。