作者:Aaron Zhang,本文转载自: Ingdan FPGA微信公众号

一 1588协议简介

IEEE 1588 是一个精密时间协议 (PTP),用于同步计算机网络中的时钟。在局域网中,它能将时钟精确度控制在亚微秒范围内,使其适于测量和控制系统。IEEE 1588 标准为时钟分配定义了一个主从式架构,由一个或多个网段及一个或多个时钟组成。TSN 网络中时间同步协议使用 IEEE 802.1AS 协议,它基于IEEE 1588 协议进行精简和修改,也称为 gPTP 协议。IEEE 1588 协议简称精确时钟协议 PTP(Precision TimingProtocol),它的全称是“网络测量和控制系统的精密时钟同步协议标准”(IEEE 1588Precision Clock Synchronization Protocol)。其工作的基本原理,是通过主从节点之间进行同步数据帧的发送,记录数据帧的发送时间和接收时间信息进行,并且将该时间信息添加到该数据帧中。从节点获取这些时间信息,并计算从节点本地时钟与主时钟的时间偏差和网络节点之间的传输延时,对本地时钟进行纠正,使之与主节点时钟同步。一个 PTP 网络只能存在一个主时钟。PTP 协议主要分为两大部分来实现时钟同步功能:1、建立同步体系:协议使用最佳主时钟算法(Best Master Clock Algorithm,BMCA),通过选取主时钟,建立主从拓扑关系,进而在整个 PTP 网络中建立起同步体系;2、同步本地时钟:协议使用本地时钟同步算法(Local Clock Synchronization Algorithm,LCS),通过 PTP 数据报文在网络主从节点之间的交换,计算各从节点本地时钟与主时钟间的时间偏差,调整本地时钟,使之与主时钟同步。

IEEE 1588将整个网络内的时钟分为两种,即普通时钟(Ordinary Clock,OC)和边界时钟(Boundary Clock,BC),只有一个PTP通信端口的时钟是普通时钟,有一个以上PTP通信端口的时钟是边界时钟,每个PTP端口提供独立的PTP通信。其中,边界时钟通常用在确定性较差的网络设备(如交换机和路由器)上。从通信关系上又可把时钟分为主时钟和从时钟,理论上任何时钟都能实现主时钟和从时钟的功能,但一个PTP通信子网内只能有一个主时钟。整个系统中的最优时钟为最高级时钟GMC(Grandmaster Clock),有着最好的稳定性、精确性、确定性等。根据各节点上时钟的精度和级别以及UTC(通用协调时间)的可追溯性等特性,由最佳主时钟算法(Best MasterClock)来自动选择各子网内的主时钟;在只有一个子网的系统中,主时钟就是最高级时钟GMC。每个系统只有一个GMC,且每个子网内只有一个主时钟,从时钟与主时钟保持同步。

二 1588同步基本原理

1. 时钟同步体系建立流程:

a. 初始状态,各个节点端口会在指定的时间内侦听网络中的 Sync 数据帧;若接收到 Sync 数据帧,节点端口将根据最佳主时钟算法决定端口状态。若没有收到 Sync 数据帧,该节点状态变更为 Pre_Master,并将自己假定为主时钟节点。此时节点端口状态表现为主时钟,但是并不发送 Sync 帧;

b. 端口状态在一定时间内保持Pre_Master:若在端口指定时间内接收到 Sync 数据帧,则该端口状态由最佳主时钟算法决定。若判定端口为主时钟,则将周期性地发送 Sync 帧;若判定为从时钟,则接受Sync 帧,并计算偏差,纠正本地时钟。若在该时间段内端口没有收到 Sync 数据帧,则将状态变更为主时钟,并且开始定时发送 Sync 数据帧;

C. 主时钟和从时钟的状态随着时钟性能与运行状态的变化而变化。整个流程可以如下图所示:

2. 时间同步建立流程:

图中所描述的 PTP 报文为以下几种:

a. sync 同步报文;

b. Follow_up 跟随报文;

c. Delay_req 延迟请求报文;

d. Delay_resp 延迟请求响应报文;

延迟响应同步机制的报文收发流程:

a. 主时钟周期性的发出 sync 报文,并记录下 sync 报文离开主时钟的精确发送时间 t1;此处 sync 报文是周期性发出,可以携带或者不携带发送时间信息,因为就算携带也只能是预估发送时间戳 originTimeStamp;

b. 主时钟将精确发送时间 t1 封装到 Follow_up 报文中,发送给从时钟;由于 sync 报文不可能携带精确的报文离开时间,所以我们在之后的 Follow_up 报文中,将 sync 报文精确的发送时间戳 t1 封装起来,发给从时钟;

c. 从时钟记录 sync 报文到达从时钟的精确时到达时间 t2;

d. 从时钟发出 delay_req 报文并且记录下精确发送时间 t3;

e. 主时钟记录下 delay_req报文到达主时钟的精确到达时间 t4;

f. 主时钟发出携带精确时间戳信息t4 的 delay_resp 报文给从时钟;

这样 从时钟处 就得到了 t1,t2,t3,t4 四个精确报文收发时间。

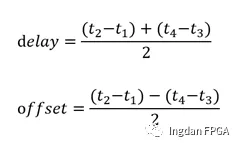

时钟偏差 & 网络延时:

offset :时钟间偏差(主从时钟之间存在时间偏差,偏离值就是 offset,图1 中主从时钟之间虚线连接时刻,就是两时钟时间一致点);

delay :网络延时(报文在网络中传输带来的延时);

从时钟可以通过 t1,t2,t3,t4 四个精确时间戳信息,得到主从时钟偏差 offset 和传输延时 delay:

从时钟得到 offset 和 delay 之后就可以通过修正本地时钟进行时间同步。

PTP报文分类:

IEEE1588 把所涉及到的报文分为 事件报文和通用报文,分类依据是:是否在收发报文时需要记录精确时间戳,根据上文中所描述的几种报文,可以进行如下分类:

事件报文 < 收发时候需要记录精确时间戳 > :sync报文,delay_req 报文;

通用报文 < 收发时候不需要几率精确时间戳 > :follow_up报文,delay_resp 报文;

Note

(1)因为需要高同步精度,选取的时间都是精确时间戳。

(2)sync 同步报文是周期性从主时钟向从时钟以广播的形式发出。

(3)时钟偏差延时的计算在从时钟中进行,所以需要把 t1,t2,t3,t4 四个时间戳信息都发往从时钟,所以需要 follow_up 报文和 delay_resp 报文的存在。

三 基于ZYNQ7000的1588实现

Xilinx ZYNQ7000系列器件包含PL和PS两部分,其中PL部分可以用FPGA逻辑实现硬化的GMII/RGMII接口,125Mhz的主时钟可以更为精确的处理网口过来的1588数据包,PS部分主要实现1588相关计算,然后将延时和数据配置到PL侧,使用千兆网口来实现1588从端经过实测可以达到单跳±100ns以内的精度,多跳场景下基本可以维持±150ns的精度。

在该案例中选用的是XC7Z020-2CLG484I器件,RGMII接口调用了Xilinx的IP来实现,整体系统的主时钟为125Mhz,整个设计的逻辑资源占用情况如下图所示:

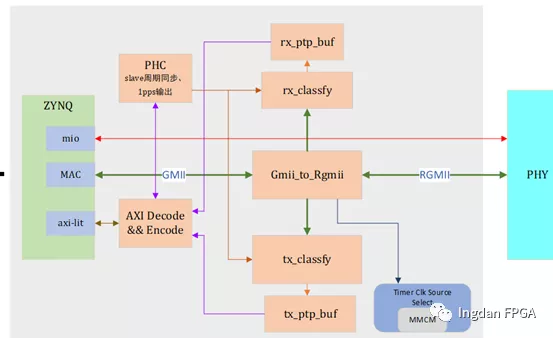

1. 整个FPGA实现框图如下所示:

PL层实现:网口协议转换,ptp协议报文识别与过滤,硬件时间戳打取,时间戳存储,时钟恢复与管理,从端主时钟实现与调整,1pps输出等功能;

PS层实现:千兆以太网MAC,Ptp1588协议实现,PHY芯片管理等功能;

2. 各个主要功能模块的功能简要介绍如下:

a. 接收方向包识别及打戳模块(rx_classfy):rx_classfy完成对以太网输入数据ptp协议报文解析,如若是ptp协议数据,在包头处打时间戳,将该时间戳信息写入rx_ptp_buf中。支持ieee802.3/TCPIP/UDP等网络格式数据。

b. 发送方向包识别及打戳模块(tx_classfy):tx_classfy完成对以太网输出数据ptp协议报文解析,如若是ptp协议数据,在包头处打时间戳,将该时间戳信息写入tx_ptp_buf中。支持ieee802.3/TCPIP/UDP等网络格式数据。

c. 接收方向时戳缓存模块(rx_ptp_buf):rx_ptp_buf完成接收方向时戳缓存。

d. 发送方向时戳缓存模块(tx_ptp_buf):tx_ptp_buf完成发送收方向时戳缓存。

e. RGMII与GMII网络接口转换模块(Gmii_to_Rgmii):Gmii_to_Rgmii完成PHY芯片RGMII接口与ZYNQ的GMII网络数据接口转换功能。

f. 从时钟恢复模块(PHC):PHC从时钟恢复模块,完成系统时间提供,恢复,调整,1pps输出等功能。

g. 时钟管理模块(Timer Clk Source Select):Timer Clk Source Select完成板卡驱动时钟恢复与管理功能。

h. AXI总线编译码模块(AXI Decode && Encode):AXI Decode && Encode完成PL与PS间AXI-LITE总线编码与译码功能。

3. ZYNQ PS端

ZYNQ的PS端运行了Peta-Linux操作系统,可以更好的实现设备的远程管理与远程更新功能,同时包括设备boot和对PHY芯片的初始化配置都是在PS侧完成的,包含千兆以太网MAC,ptp1588协议层,实现网络包收发,ptp协议解析,ptp包文封包,时间戳读取,PL层周期与调整值计算,PHY芯片管理等功能。

如果您在1588时钟同步方面有问题,欢迎联系: