Versal Premium 112G PAM4 GTM SERDES OFC

judy 在 周四, 07/15/2021 - 11:28 提交

Versal Premium 通过全新的 GTM SERDES 提供了 112G PAM4。 本视频对此项技术进行了概述, 并演示了 SERDES 运行于直接连接铜缆。

Versal Premium 通过全新的 GTM SERDES 提供了 112G PAM4。 本视频对此项技术进行了概述, 并演示了 SERDES 运行于直接连接铜缆。

Vitis 加速基本平台创建

近期,科通与全球头部FPGA厂商赛灵思携手雪湖科技打造的智慧交通场景设计方案,已成功在多家行业头部企业落地。科通作为服务芯片产业的技术服务平台,提供芯片的应用设计方案和销售,一直与赛灵思积极布局自动驾驶赛道。

Xilinx 的 16nm FPGA、SoC 和 7nm Versal™ ACAP 以硬化模块及软 IP 形式提供多种架构组件,这使得它们成了设计新一代安全设备的理想之选。这些 IP 包括高速串行解串器和多速率接口 IP,例如硬化 MAC、PCIe® 接口和内存控制器等。

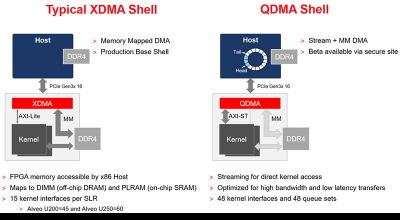

赛灵思全新流式 QDMA (队列直接存储器访问)Shell 平台现已登陆 Alveo™ 加速器卡,能够为开发者提供主机与内核间的低时延直接流连接。QDMA Shell 包含一个高性能 DMA,它使用的多个队列专为高带宽和大量包数据传输进行优化。

2021 赛灵思技术日是一场以“自适应”技术为平台的线下深度互动会议,是软件/硬件研发人员、算法开发、系统架构师的专属会议。在这里,您可以看到最新的产品工具介绍、方案与 IP 更新、应用实例展示等内容,更可以与专家面对面深入探讨从设计技巧、系统性能到架构优化等话题。

当下,Open RAN “大势渐成”。日本乐天集团计划在2021年年底前完成7000个站点的部署;美国 Dish Network 公司计划打造首个全面开放、符合 RAN 技术标准的全国性独立5G无线网络;欧洲一些最大的运营商发布了 Open RAN 系统的优先技术要求清单,以期从2022年开始大规模部署基于该架构的技术。

图文了解基于Vitis AI1.2 dpu平台测试

计算密集型应用是指需要大量复杂计算的任何计算机应用。像 AI 推理、大数据分析、网络和科学研究建模之类就是如今的一些比较流行的计算密集型应用。Xilinx UltraScale MPSoC 架构提供了多种高级处理器,从 32 位到 64 位,支持虚拟化,并通过“合适的任务使用合适的引擎”理念实现了真正的异构多处理能力。

描述使用 Vivado® Design Suite 生成加密比特流和加密密钥的分步过程。