新药研发进入算力时代,赛灵思FPGA大显身手

judy 在 周五, 08/13/2021 - 10:07 提交

在对抗疾病的战斗中,药物发挥了巨大的作用。因此,每找到一方对症的新药人类就赢得了一次对疾病的斗争!但是,新药的找寻和研究从来都是极其艰难和凶险的,中国古有神农氏尝百草寻药,但最后却被断肠草毒杀。到了近代,随着对药物的研究深入到分子层级,加上计算机的辅助,新药研制加速,但是平均下来仍然需要15年左右的时间以及20亿美元的投入。

在对抗疾病的战斗中,药物发挥了巨大的作用。因此,每找到一方对症的新药人类就赢得了一次对疾病的斗争!但是,新药的找寻和研究从来都是极其艰难和凶险的,中国古有神农氏尝百草寻药,但最后却被断肠草毒杀。到了近代,随着对药物的研究深入到分子层级,加上计算机的辅助,新药研制加速,但是平均下来仍然需要15年左右的时间以及20亿美元的投入。

Xilinx VCK5000 Versal 开发卡基于Xilinx 7nm VersalACAP架构构建,专为高吞吐量AI推理和高性能计算应用而设计。VCK5000具有标准化的软件开发流程,可提供比当今服务器级CPU高100倍的计算能力,并且比当今服务器级GPU更好的MLPerf推理性能,是云加速和边缘计算应用的理想开发平台。

本视频介绍了深度学习算法在赛灵思7nm Versal板卡上的优化与部署

随着设计复杂度和调用IP丰富度的增加,在调试时序约束的过程中,用户常常会对除了自己设定的约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,我的XDC里面并没有指定set_false_path,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的?本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试提供一些技巧和窍门。

大多数人可能没有意识到我们的设备在多大程度上是由时间驱动的,无论是你的手机、你的笔记本电脑还是网络服务器。在大多数情况下,设备保持准确的时间一直是一个深奥的苦差事,由有限的硬件制造商负责处理。虽然这些设备达到了它们的目的,但几位Facebook的工程师认为必须有一个更好的方法。

前几节已经构建好Linux系统,但控制VCU还需要了解VCU软件架构,并加入各种库文件,也就是在Petalinxu中加入配方文件。

在 XTD 活动现场,赛灵思资深 RF 和高速专家顾永国深入讲解了基于 Pynq-RFSoC 框架的开源可视化测试设备。

1984 年,Ross Freeman 将其关于现场可编程门阵列 (FPGA) 的绝妙构想付诸实践并创立了赛灵思公司,从而确立了自适应计算的原理。从那时起,这项技术及其满足众多应用需求的能力,已历经漫长的发展道路。尽管自适应计算构建在 FPGA 技术的基础上,但它已经发展至足以覆盖更为广阔的应用类型。

有工程师询问vcu-ctrl-sw里decoder的退出机制。 下面的内容,根据vcu-ctrl-sw 2020.2分析。

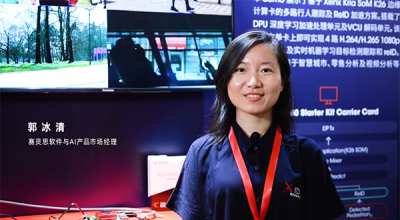

在 XTD 活动现场,赛灵思软件及人工智能市场经理郭冰清讲解了两款基于 Kria SOM 平台的 demo 演示,包括实时人脸检测,以及多路 ReID 边缘加速计算盒。