基于 PYNQ-RFSoC 框架的开源可视化测试设备

judy 在 周四, 08/12/2021 - 09:35 提交

在 XTD 活动现场,赛灵思资深 RF 和高速专家顾永国深入讲解了基于 Pynq-RFSoC 框架的开源可视化测试设备。

在 XTD 活动现场,赛灵思资深 RF 和高速专家顾永国深入讲解了基于 Pynq-RFSoC 框架的开源可视化测试设备。

1984 年,Ross Freeman 将其关于现场可编程门阵列 (FPGA) 的绝妙构想付诸实践并创立了赛灵思公司,从而确立了自适应计算的原理。从那时起,这项技术及其满足众多应用需求的能力,已历经漫长的发展道路。尽管自适应计算构建在 FPGA 技术的基础上,但它已经发展至足以覆盖更为广阔的应用类型。

有工程师询问vcu-ctrl-sw里decoder的退出机制。 下面的内容,根据vcu-ctrl-sw 2020.2分析。

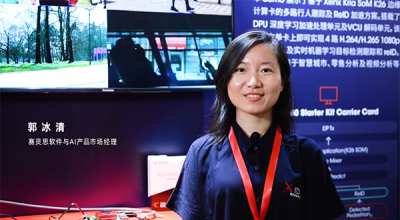

在 XTD 活动现场,赛灵思软件及人工智能市场经理郭冰清讲解了两款基于 Kria SOM 平台的 demo 演示,包括实时人脸检测,以及多路 ReID 边缘加速计算盒。

靠近模拟-数字边界边缘节点的位置对真实环境的即时响应受高度重视,众多市场领域存在迫切需求。Versal™ ACAP 产品组合 AI Edge 系列则应运而生,作为一种领域专用架构 (DSA),有效满足 7nm 芯片工艺系统提出的严苛要求。

如果是VCK190 ES单板,需要在Lounge里申请"Versal Tools Early Eacess"; "Versal Tools PDI Early Eacess"的License,并在Vivado里使能ES器件。在Vivado/2020.2/scripts/init.tcl的文件里,添加“enable_beta_device xcvc*”,可以自动使能ES器件。

FZU5构建Linux系统过程和FZU3类似,FZU3构建过程参照前一篇文章。下面主要描述一下不同的地方。

Xilinx 的 16nm FPGA、SoC 和 7nm Versal™ ACAP 以硬化模块及软 IP 形式提供多种架构组件,这使得它们成了设计新一代安全设备的理想之选。这些 IP 包括高速串行解串器和多速率接口 IP,例如硬化 MAC、PCIe® 接口和内存控制器等。此外,Xilinx 器件还可提供业界一流的最新内存架构,其可为流程分类提供软搜索 IP,因此最适合网络安全与防火墙应用。

作为赛灵思(Xilinx)在疫情之后在北京举办的首场大型线下活动,今年赛灵思技术日特意将主题选定为“‘适’逢芯动,聚创未来”。赛灵思大中华区核心市场销售副总裁唐晓蕾在接受《电子工程专辑》独家专访时表示,虽然只有短短的八个字,但背后所蕴含的,是赛灵思希望在当前复杂多变的环境下,通过自适应计算平台汇集数据、汇聚生态,加速创新的美好愿景。

FPGA在人工智能领域,突破了“暗硅”为我们带来了更强大的可能性。现在依元素科技提供了一个完整的FPGA加速解决方案,让AI工程师能够以“即插即用”的方式部署 FPGA,AI 工程师隐藏了 FPGA,不需要硬件细节,让他们享受更快的执行。