软硬兼施赋能 Open RAN 大规模部署

judy 在 周三, 07/21/2021 - 13:22 提交

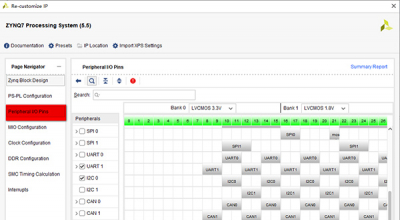

“软硬兼长”是京信与赛灵思合作的基础,也是更好赋能 Open RAN 的一大关键。自2007年初以来,京信随即开始采用赛灵思芯片及解决方案,并随其演进步伐持续开发高质量无线电产品及系统。赛灵思 Artix 7 系列 FPGA 广泛用于京信 2G/3G/4G 传统产品线。伴随 5G 时代的到来,赛灵思 Zynq 7000 SoC、MPSoC、Kintex 系列已广泛应用于京信新一代高效无线产品。