Open RAN 大势渐成,规模部署迫在眉睫

judy 在 周三, 07/14/2021 - 09:28 提交

当下,Open RAN “大势渐成”。日本乐天集团计划在2021年年底前完成7000个站点的部署;美国 Dish Network 公司计划打造首个全面开放、符合 RAN 技术标准的全国性独立5G无线网络;欧洲一些最大的运营商发布了 Open RAN 系统的优先技术要求清单,以期从2022年开始大规模部署基于该架构的技术。

当下,Open RAN “大势渐成”。日本乐天集团计划在2021年年底前完成7000个站点的部署;美国 Dish Network 公司计划打造首个全面开放、符合 RAN 技术标准的全国性独立5G无线网络;欧洲一些最大的运营商发布了 Open RAN 系统的优先技术要求清单,以期从2022年开始大规模部署基于该架构的技术。

图文了解基于Vitis AI1.2 dpu平台测试

计算密集型应用是指需要大量复杂计算的任何计算机应用。像 AI 推理、大数据分析、网络和科学研究建模之类就是如今的一些比较流行的计算密集型应用。Xilinx UltraScale MPSoC 架构提供了多种高级处理器,从 32 位到 64 位,支持虚拟化,并通过“合适的任务使用合适的引擎”理念实现了真正的异构多处理能力。

描述使用 Vivado® Design Suite 生成加密比特流和加密密钥的分步过程。

了解块设计容器及其兼容性。

Xilinx OpenAMP 框架入门指南。

如果您计划开发一个无线应用程序,并且需要选择一款软件无线电(SDR),您可能会面临一些疑问,例如:我从何处入手?哪一款通用软件无线电外设(USRP)适合我?我应该使用哪种软件开发工具?本技术白皮书介绍了各种USRP型号之间的主要差异,可以帮助您选择合适的无线电。

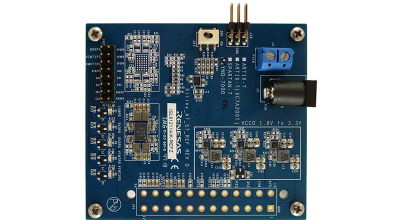

Zynq-7000 设备的 ISL91211AIK-REFZ 参考板采用 ISL91211AIK 多相 PMIC、ISL9123 低静态电流升降压稳压器和两个 ISL80030 3A 同步降压 DC/DC 变换器。VCCINT、VCCBRAM、VCC_DDR 和 VCCAUX 需要 ISL91211AIK。

在本视频中,我们展示了在 XCZU47DR 器件的双模块中使用两个 5GSPS ADC 的 10GSPS ADC 性能。

应用程序不断增多,适用的无线设备也随之增加,造成需求和设计越发复杂。由于人们需要的数据越来越多,硬件设计便向着更宽的带宽、更高的频率和更多的通道发展,而软件则需要提供更大的灵活性,并缩短产品上市时间