由繁入简,Kria SOM 突破嵌入式设计障碍!

judy 在 周四, 06/03/2021 - 11:14 提交

我们常说“大道至简”,因为往往用词越多,想法就越具体、越琐碎,所以当我们在开发 Kria™ SOM (System-on-Module,系统模块) 时,就大胆提出了“无需 FPGA 设计也可尽享赛灵思技术优势”这一概念。

我们常说“大道至简”,因为往往用词越多,想法就越具体、越琐碎,所以当我们在开发 Kria™ SOM (System-on-Module,系统模块) 时,就大胆提出了“无需 FPGA 设计也可尽享赛灵思技术优势”这一概念。

在这两个小时的活动中,赛灵思携手生态系统合作伙伴将为您带来一场专门为广播、专业音视频和消费电子构建的技术、IP 和解决方案的技术峰会。

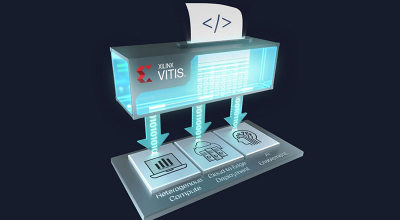

在Vitis 统一软件平台中使用Alveo系列开发板设计加速Kernel时,系统会自动为Kernel的时钟设置默认频率。以 xilinx_u200_qdma_201910_1 平台为例,在Vitis中选择平台时可以看到默认的时钟频率是300Mhz和500Mhz。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件

TTC 包含三个独立的定时器/计数器,PS中有两个TTC模块,总共有六个定时器/计数器,TTC 1 控制器可以配置为安全或非安全模式,使用nic301_addr_region_ctrl_registers.security_apb [ttc1_apb] 寄存器位。TTC 控制器内的三个定时器具有相同的安全状态。

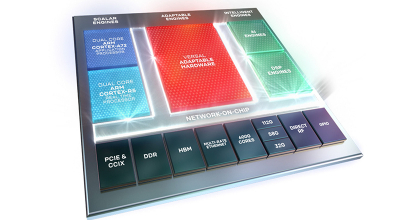

本视频将分享一下异构的百万兆计算的发展方向,赛灵思技术将发挥和正在发挥的重要作用。

在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

Arm Cortex-R5F 处理器包含 1 个 4 输入存储缓冲器,用于对数据先进行缓冲、合并和转发,然后再使用 AXI 主接口将数据写入高速缓存或 L2 存储器系统。由于此错误,存储缓冲器可能进入所有现有写入都无法继续执行的状态。此状态可能会导致下列问题:

本视频将介绍自适应计算技术的未来。

利用SDR做一个收音机是所有入门SDR都会做的小项目,简单直观易上手的特点和“Hello World”、流水灯一样。本篇文章就带领大家利用AD936X+ZYNQ平台SDR做个SDR。