直播 | 如何在Alveo Versal上快速部署AI推断 - VCK5000助力软件/AI开发升级

judy 在 周五, 05/21/2021 - 09:30 提交

赛灵思近期推出重磅活动,2495 美元的优惠价购买用于 AI 推断的 VCK5000 Versal™ 开发卡,VCK5000 的计算能力比当前的服务器级 CPU 高 100 倍,MLPerf 推断性能也高于当前的服务器级 GPU,是云加速和边缘计算应用的理想开发平台。

赛灵思近期推出重磅活动,2495 美元的优惠价购买用于 AI 推断的 VCK5000 Versal™ 开发卡,VCK5000 的计算能力比当前的服务器级 CPU 高 100 倍,MLPerf 推断性能也高于当前的服务器级 GPU,是云加速和边缘计算应用的理想开发平台。

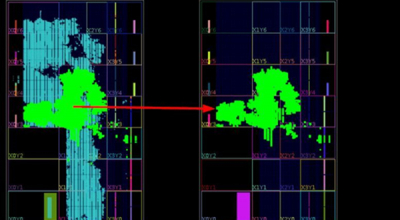

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。 今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别。

近日,赛灵思总裁兼首席执行官Victor Peng在收购后首次亮相,隔着太平洋与中国媒体交流了后摩尔时代的计算趋势,系统梳理了赛灵思与AMD在数据中心的发展优势以及产品战略,也解答了很多大家关心的这几个问题。

本视频说明了如何使用 Xilinx 功耗估算器工具预测 Zynq®UltraScale +™RFSoC 的 RF 数据转换器 IP 的功耗。

针对流媒体行业不断增长的需求,专业音视频处理设备和解决方案供应商 RGBlink 推出了 mini 和 mini+ 推流切换台。这些为 IP 视频流应用量身定制的小型信号切换器设备,为普通消费者享受专业的音视频技术打开了大门。该设备基于赛灵思的 Artix®-7 7A200T 平台构建。

人工智能发展迅速,创新步伐不断加快。然而,虽然软件行业已经成功在生产中部署了 AI,但包括汽车、工业和智能零售等在内的硬件行业,在 AI 产品化方面仍处于初级阶段。阻碍 AI 算法概念验证 (PoC) 成为真正硬件部署的主要差距仍然存在。

5G 产业潜力巨大,但行业如何才能克服成本、功耗与性能等相关挑战,确保 5G 在第二次浪潮中大获成功?无线行业的未来取决于是否能够综合运用先进技术最大化系统性能,同时最优化成本与功耗以提供极具竞争力的产品。

今年 4 月,赛灵思取得了令人激动的阶段性成果,即宣布实现 Versal™ AI Core 系列和 Versal Prime 系列的全面量产和付运。对于 Versal Prime 系列而言,这意味着 Vm1xxx 的首批量产器件进入供货状态;VM1xxx 器件可支持 PCIe® Gen 4 和 32G GTY 收发器

5月26日 14:00,赛灵思数据中心事业部总经理 Salil Raje 将向您介绍自适应计算技术 – 可组合式数据中心。将为您详细介绍 “可组合式数据中心”,以及 FPGA 是如何解决上述的挑战,从而为业界提供一个加速的,灵活可扩展的自适应方案。