280MHz 全频段 C-band解决方案来了

judy 在 周六, 05/08/2021 - 10:58 提交

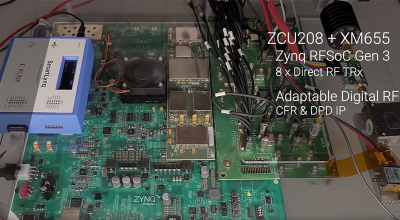

为展现赛灵思芯片和射频 IP 的可扩展能力,赛灵思与 Skyworks 公司共同协作,带来基于赛灵思第三代 RFSoC 器件和 Skyworks SKY66523-11 功率放大器的280MHz 全频段 C-band 瞬时带宽解决方案。

为展现赛灵思芯片和射频 IP 的可扩展能力,赛灵思与 Skyworks 公司共同协作,带来基于赛灵思第三代 RFSoC 器件和 Skyworks SKY66523-11 功率放大器的280MHz 全频段 C-band 瞬时带宽解决方案。

随着以人工智能技术为代表的数字经济浪潮的来临,如今,AI 正越来越多地被部署于边缘应用,这些应用要求以低时延、低功耗和小封装尺寸执行大量数据处理。要想实现这一综合要求就必须为整体 AI 流程和非 AI 流程都进行提速,这也要求加速平台必须具备灵活应变的能力。

AI 作为当下的热门行业,蕴藏着巨大的市场机会与风险挑战,而面对这样的新兴领域,无论是专业人士或是企业都需要不断交流学习,从而激发灵感,加速创新。5 月 20 日,安富利将携手赛灵思在内的合作伙伴举办“安富利 AI 云展会”,全方位展示 AI 和机器学习领域的创新技术、应用和解决方案。

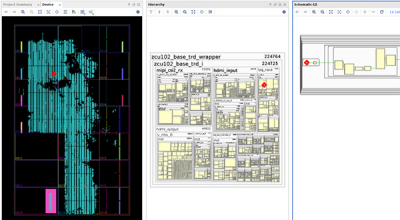

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

本视频将探讨Vivado IP集成器的特效与优势以及它如何帮助您解决复杂的设计问题。

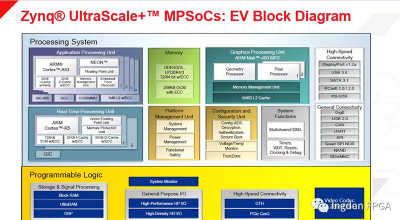

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

fpga 上电时,默认是从 flash 的 0x00 地址开始读数据。如 UG470 文档 page144 描述

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线。比如在文件xfsbl_partition_load.c中,FSBL加载FPGA的bit后会执行下列操作,打开PS和PL之间的接口和信号线

本视频介绍Versal自适应计算加速平台ACAP。介绍了Versal中的仿真和调试功能。

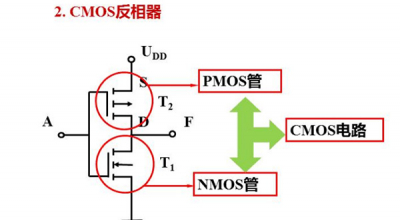

CMOS与非门,只要有一个输入端为低电平,与运算后均为低电平,输出为高电平,影响了输出结果,若接地或悬空会使输出始终为 1。CMOS与门、与非门:多余端通过限流电阻(500Ω)接电源;CMOS或门、或非门:多余端通过限流电阻(500Ω)接地;