【Vitis指南】Xilinx Vitis 系列(三)

judy 在 周三, 04/14/2021 - 10:32 提交

今天带来第三篇,介绍使用Vitis分析仪。Vitis分析仪是一种实用工具,允许查看和分析,同时建立并运行应用程序生成的报告。旨在查看由构建应用程序时的Vitis编译器和运行应用程序时的Xilinx®Runtime(XRT)库生成的报告。

今天带来第三篇,介绍使用Vitis分析仪。Vitis分析仪是一种实用工具,允许查看和分析,同时建立并运行应用程序生成的报告。旨在查看由构建应用程序时的Vitis编译器和运行应用程序时的Xilinx®Runtime(XRT)库生成的报告。

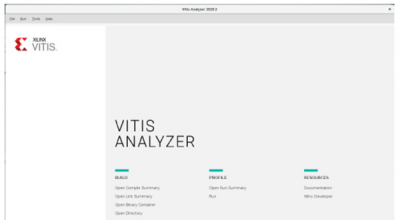

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

本文描述在Vivado®工具中使用Xilinx®设计约束(XDC)。XDC结合了行业标准的Synopsys设计约束(SDC)和Xilinx专有约束。创建XDC来定义时钟,I / O延迟和时序异常(如错误和多周期路径以及最小/最大延迟)的详细信息。

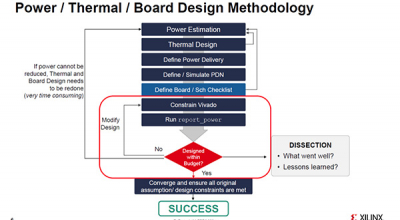

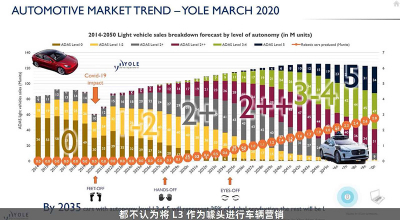

本视频介绍使用人工智能的计算和汽车的市场范围。讨论汽车行业的处理器市场从离散标量处理器到大规模异构平台的发展。深入探讨高级辅助驾驶和自动驾驶之间的区别,并作出一个预测。

本文介绍 Vivado® 集成设计环境 (IDE),它提供了直观的图形用户界面 (GUI),用于可视化和与 FPGA 设计交互。描述了Vivado IDE如何帮助您配置工具选项、分析和完善时序,以及设计平面图以改进结果。

今天带来第一篇,介绍Vitis 2019.2软件平台发行说明、安装以及Vitis加速环境简介。

作为全球唯一基于16纳米技术的成本优化型产品组合,UltraScale+ 器件采用台积电最先进的InFO(Integrated Fan Out,集成扇出)封装技术。借助InFO技术,UltraScale+ 器件能以紧凑的封装提供高计算密度、出色的性能功耗比以及可扩展性,从而应对智能边缘应用的需求。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。

本文详细介绍Vivado工具中Tcl脚本的使用,查询和修改自定义流程的内存设计。讨论如何使用Tcl过程来定义和共享自定义命令。提供了遍历设计层次结构、访问设计对象和处理自定义报告的步骤。