赛灵思Vitis AI开发环境的正确安装姿势

joycha 在 周五, 03/26/2021 - 16:27 提交

赛灵思Vitis AI开发环境的正确安装姿势

赛灵思Vitis AI开发环境的正确安装姿势

Xilinx自适应器件的灵活性和可配置性与IP和工具产品相结合,可显著提高安全处理性能。

本视频快速介绍 Vitis AI Model Zoo 的计划和内容,包括全新 1.3 版本中的新增功能。

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

Alveo 加速卡除了有我们 ultrascale+系列的芯片以外,还有 TI 的 MSP432,它的作用就是监控板子的状态,比如电流电压温度等信息。主控端可以通过 FPGA,访问 MPS432,然后获取这些信息。那么怎么样简单的获得这些信息呢,为此我们准备了 CMSIP。

本视频介绍了Vitis和Vitis-AI,将重点讲解Vitis-AI的设计流程以及如何在边缘和云端器件上进行部署。

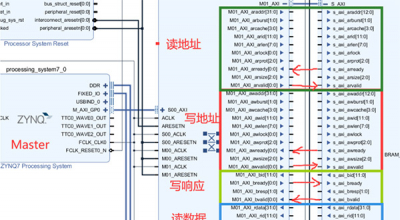

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间双向传输,且数据传输大小可以不同。AXI4中的限制是一个突发事务(Burst)最多可以传输256个数据,AXI4-Lite只允许每个事务传输1个数据。

作为音视频行业各种设备制造商的供应商,客户经常会来咨询,我们认为哪一种 IP 音视频传输标准将最终胜出。我们看到广播行业曾经出现过这样的不确定性和混乱时期。当时存在多项相互竞争的协议,竞相角逐同样的应用,造成整个行业在一段时间里踌躇不前,发展停滞。

在探索宇宙的道路上,无数顶尖的科学家、企业都为之做出了自己的贡献。可以说,人类对宇宙的征途,是所有相关人员、企业的智慧结晶。作为自适应计算的领军者,赛灵思在充满未知的宇宙探索领域,贡献了不可忽视的力量。

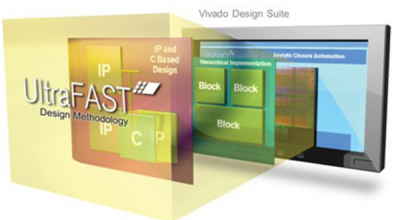

赛灵思 UltraFast™ 设计方法旨在帮助简化当今器件设计进程的最佳实践,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛提供推荐方法背后的原理,以支持用户制定出明智的设计决策。