【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章 PS端DP的使用

judy 在 周四, 01/28/2021 - 09:47 提交

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

在不平凡的2020年,智能化引领汽车产业带来崭新变革,站在2021年的新起点上,基于对自动驾驶汽车技术的不断深入探索,赛灵思将在汽车领域开拓一片新天地,而汽车产业也将继续拥抱新技术与新方法,为实现自动驾驶奠定基石!汽车产业在 2021 年将面临哪些新挑战,迎接哪些新变化?2021年 3月3日 至 3月5日,“Xilinx Adapt China: 汽车电子” 将为你完整解读。

SmartLynq+ 模块的构建旨在满足高速调试和跟踪需求,主要面向使用 Versal™ 平台的开发者。与以前的赛灵思调试产品相比,SmartLynq + 模块通过 HSDP 可将 Linux下载时间最多提高28倍,并将数据捕获速度提高100倍。

在本期分享会中,赛灵思将联合拥有十多年专业音视频产品及解决方案研发经验的厦门 RGBlink 视诚科技公司,针对赛灵思视频解决方案的组合、特性及市场价值等话题进行分享和探讨

本视频将通过示例应用介绍如何借助Vitis和Vitis AI加速实时AI推断。

本文描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。

本视频将介绍Vitis HLS产品以及支持从基于C语言开始对FPGA进行编程的底层技术。

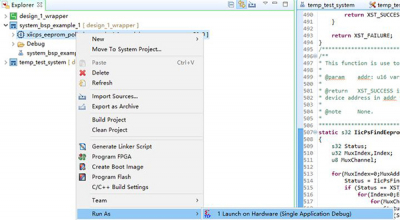

PS端I2C的使用

若您的浏览器不支持插件,请前往 Bilibili 观看视频

|

|