赛灵思FPGA助力安全自动驾驶“三重视觉”:激光雷达

judy 在 周一, 01/11/2021 - 09:57 提交

据麦姆斯咨询报道,得益于高级驾驶员辅助系统(ADAS),例如自动紧急制动(AEB)和驾驶员监控系统(DMS),汽车变得越来越安全。随着这些功能的复杂性增加,也让自动驾驶给予人类越来越高的安全感。例如,AEB最初只能探测汽车前进方向的危险,如今已发展到可以探测行人、交叉口交通、自行车骑行者和道路障碍物。

据麦姆斯咨询报道,得益于高级驾驶员辅助系统(ADAS),例如自动紧急制动(AEB)和驾驶员监控系统(DMS),汽车变得越来越安全。随着这些功能的复杂性增加,也让自动驾驶给予人类越来越高的安全感。例如,AEB最初只能探测汽车前进方向的危险,如今已发展到可以探测行人、交叉口交通、自行车骑行者和道路障碍物。

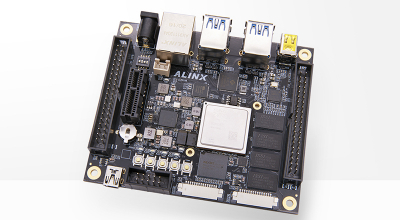

本章以AN3485模块介绍RS485的数据传输。

装备业界首个自适应计算加速平台(ACAP)的赛灵思 Versal AI Core 系列 VCK190评估套件 和 Versal Prime 系列 VMK180 Prime 评估套件,现已上市!VCK190 是赛灵思首款 Versal™ AI Core 系列评估套件,可帮助设计者使用 AI 和 DSP 引擎开发解决方案,与当前服务器级 CPU 相比,该解决方案可将计算性能提升 100 多倍!

在本文中,我们将进一步采取主动行动,以解决网络核心(交换机)中当前的专有处理和计算问题。我们提出了一种新的硬件架构,称为自适应交换机。基于对其支持三个用例的原型的测试,我们证明了在可适应的交换机上可以同时实现高吞吐量和处理灵活性。

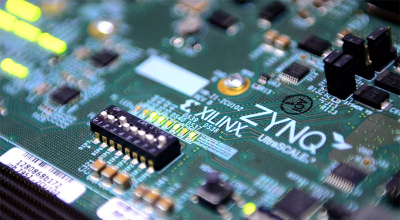

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

在开发以太网接口的过程中经常看到 MII、RMII、GMII、RGMII等英文缩写名称。在开发接口前,先将这些名词搞清楚。

HLS 优化设计的最关键指令有两个:一个是流水线 (pipeline) 指令,一个是数据流(dataflow) 指令。正确地使用好这两个指令能够增强算法地并行性,提升吞吐量,降低延迟但是需要遵循一定的代码风格。

在 1月19日 的线上研讨会上,我们将邀请赛灵思软件与 AI 部门的专家与大家分享集成了 AI 引擎的 Versal AI Core 器件与 CPU/ GPU / FPGA 的算力比拼;Versal AI Core 在自动驾驶、机器学习、智慧医疗等领域的实际案例;另外,还有最新发布的 Vitis 1.3 的十大亮点功能的分享和探讨。干货满满,不容错过。

本章利用AN3485模块实现RS422接口数据传输。关于模块,在前面的RS232实验中已经介绍过,本实验不再赘述。RS422与RS232在与FPGA的连接的接口上是一样的,都是TXD和RXD,因此,本实验在RS232实验的基础上,例化出两路连接到RS422接口芯片MAX3490上

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景