1024bit以上大位宽可重构包处理器可编程CRC算法的设计与实现

judy 在 周三, 12/30/2020 - 15:35 提交

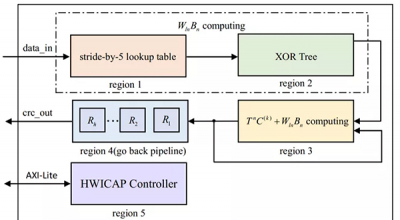

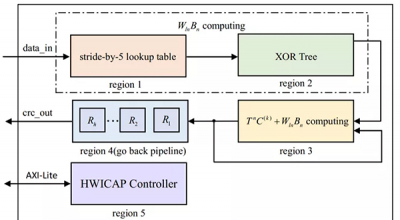

循环冗余码校验(CRC)是一种众所周知的错误检测代码,已广泛用于以太网,PCIe和其他传输协议中。现有的基于FPGA的实现解决方案在高性能场景中会遇到资源过度利用的问题。填充零问题和可编程性的引入进一步加剧了这个问题。在本文中,提出了stride-by-5算法,以实现FPGA资源的最佳利用。提出了pipelining go back算法来解决填充零问题。

循环冗余码校验(CRC)是一种众所周知的错误检测代码,已广泛用于以太网,PCIe和其他传输协议中。现有的基于FPGA的实现解决方案在高性能场景中会遇到资源过度利用的问题。填充零问题和可编程性的引入进一步加剧了这个问题。在本文中,提出了stride-by-5算法,以实现FPGA资源的最佳利用。提出了pipelining go back算法来解决填充零问题。

FPGA本身是SRAM架构的,断电之后,程序就消失,那么如何利用FPGA实现一个ROM呢,我们可以利用FPGA内部的RAM资源实现ROM,但不是真正意义上的ROM,而是每次上电都会把初始化的值先写入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。

规模稍微大一点的FPGA工程的警告和critical warning动辄两三千条,虽然其中包含大量的“无威胁”警告和重复警告,但是我觉得至少95%的程序隐患和设计问题都可以从这些报告中找到蛛丝马迹。

DONE 变为高电平后应给 CCLK 应用多少个时钟周期以确保我的 FPGA 器件完全工作。

自动驾驶发展至今,在更加严格的安全等级和功耗成本限制下,实现高级自动驾驶,对充当自动驾驶“大脑”的域控制器提出了更高的要求。除了特斯拉等业界巨头,能够在这个领域落地的方案可谓凤毛麟角。而成立于 2018 年的宏景智驾,便是这个高级自动驾驶赛道的领先探险者之一。

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4 存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应

广岛大学采用赛灵思 Alveo U250 加速器卡,加速了基于图像且以机器学习推断为特性的癌症诊断解决方案。让我们看看他们是怎么做的吧。

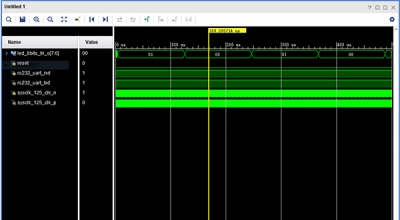

本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

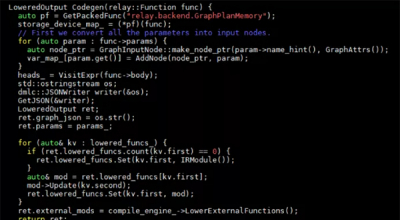

接着上一章继续深入代码,在BuildRelay中会调用Codegen函数。这个函数实现在src/relay/backend/graph_runtime_codegen.cc中。Codegen实现了内存的分配,IR节点到TIR节点的转换,tir图节点的一个调度优化。

PYNQ框架的设计初衷是通过高层次的封装,将底层硬件FPGA实现细节与上层应用层的使用脱耦,对软件开发者来说,PYNQ框架已经提供了完整的访问FPGA资源的library,让上层应用开发者通过Python编程就可以调用FPGA模块,不需要懂Verilog/VHDL硬件编程就可以享受FPGA可并行计算、接口可方便扩展和可灵活配置带来的诸多好处