【Vivado那些事】Vivado下头文件使用注意事项

judy 在 周四, 12/17/2020 - 11:17 提交

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

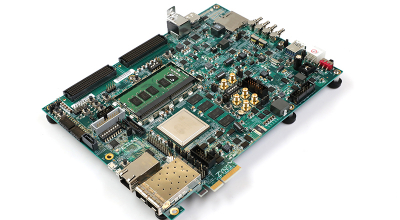

Xilinx拥有非常广泛的产品组合,涉及非常多的细分市场,并提供了各种各样的部署方法,因此对于刚接触FPGA的新手来说,可能很难了解“全局”。

利用 Vitis 释放新的设计体验,并利用 Xilinx 自适应平台的强大功能实现边缘到云的部署。

一直以来,FPGA 只能用硬件描述语言(RTL)编程 —— 真的是这样吗?未必!!参加 Xilinx Adapt: SW & AI (1 月 7 日 - 8 日) ,了解赛灵思如何在包括 TensorFlow 和 PyTorch 在内的流行软件开发平台中支持 AI/ML 加速的。

12月23日,19:30 – 21:00,我们邀请腾讯云微瓴即视产品经理钟赛和傲睿智存科技CEO廖玉峰以实际部署案例,来帮助广大系统工程师,算法工程师和软硬件设计工程师树立FPGA在视频和AI应用领域的正确定位,带您浅入深出的了解如何用赛灵思 FPGA 玩转 Video + AI。

人工智能和机器学习的进步早已超越了CPU性能的提升速度,硬件加速愿景美好,开发却曲高和寡。如何打破软硬件语言壁垒,提升开发效率?

智能驾驶驱动的汽车行业正在走向电气化时代,全球各大车企都在加速电气化进程。未来智能驾驶将朝有哪些关键技术发展,有哪些阻碍发展的痛点,如何解决?以下为本刊独家采访赛灵思汽车电子系统架构师毛广辉实录。

Xilinx为MPSoC支持4种libMali的backend: X11, Wayland/GBM, Fbdev, Headless-EGL。QT支持4种plugin(插件)或者backend,FB,X11,Wayland,eglfs。对不同的plugin(插件)或者backend,QT应用层是一样的。

基于UltraScale架构的FPGA的封装和引脚规格不同。包括7系列FPGA在内的前几代产品。这些细节在此概述。

InAccel 的 Accelerated Machine Learning Studio(AML)是一个完全集成的框架,可在不更改代码的情况下加速 C / C ++、Python、Java 和 Scala 应用。