Confinity 低延时消息传递 (CLLM)解决方案

judy 在 周一, 10/26/2020 - 10:06 提交

CLLM 4.0 是在 Xilinx Alveo 板上运行的硬件加速低延迟消息传递解决方案。

CLLM 4.0 是在 Xilinx Alveo 板上运行的硬件加速低延迟消息传递解决方案。

国微思尔芯正式推出面向超大规模 SoC 原型市场的 ProdigyTM S7-19P 原型验证系统。 S7-19P 提供单、双、四核 Xilinx UltraScale+ VU19P FPGA 配置,搭配同时发布的 Player Pro 编译软件可以轻松满足如 5G、数据中心、AI/ML 和自动驾驶等大规模 SoC 设计中不断增加的复杂性和性能等验证需求

依元素科技将基于边缘端MPSOC器件(以ZCU104开发板为例),通过为期半天的在线讲座,结合动手实验操作,引领开发者快速搭建基于Vitis AI的DPU开发环境,并通过图像和视频的实际应用开发实例,了解DPU开发的整个流程及其功能特性。

本文介绍如何将低功率域 (LPD) 作为一个通道和 PL 中的一个三模冗余 MicroBlaze 来创建和实现单片通用 2 通道系统。

无论是设计测试和测量设备还是汽车激光雷达模拟前端(AFE),使用现代高速数据转换器的硬件设计人员都面临高频输入、输出、时钟速率和数字接口的严峻挑战。问题可能包括与您的现场可编程门阵列(FPGA)相连、确信您的首个设计通道将起作用或确定在构建系统之前如何对系统进行最佳建模。

Zynq UltraScale + RFSoC Gen 3 器件是业界唯一的第三代单芯片自适应射频平台,该平台全面支持 6GHz 以下直接 RF。 该视频展示了 Zynq UltraScale + RFSoC ZU49DR 16x16 器件以 6 GHz 传输 256 个 QAM 信号的卓越信号质量和性能。

本设计咨询涵盖了如下实现问题:时钟在驱动 UltraScale 或 UltraScale+ 架构的物理层块 (PHY) 时可能执行错误的反相操作。使用 Vivado 2020.1 或 Vivado 2020.1.1 时,PHY BITSLICE site 中包含的可选反相器 IPHY_OCLK_OPTINV 基于 INVERT 属性可能执行错误的反相操作。

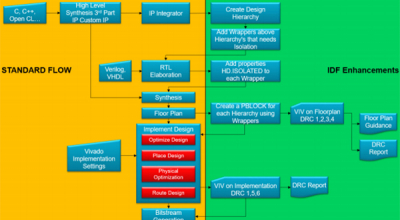

在单个器件中集成安全/非安全功能成为可能。Xilinx提供当今一流的工具和技术,使IEC/ISO安全认证成为可能。

本设计咨询涵盖了如下实现问题:时钟在驱动 UltraScale 或 UltraScale+ 架构的物理层块 (PHY) 时可能执行错误的反相操作。

使用 Vivado 2020.1 或 Vivado 2020.1.1 时,PHY BITSLICE site 中包含的可选反相器 IPHY_OCLK_OPTINV 基于 INVERT 属性可能执行错误的反相操作。

ZDMA应用例子xzdma_simple_example.c 缺省只运行一次。在XZDma_SimpleExample()里的XZDma_SelfTest( )之后,把运行部分放进一个循环体,可以多次运行。测试工具是Xilinx SDK 2018.2.