UltraScale+ 器件 Integrated Block for PCI Express v1.3 产品指南(中文版)

judy 在 周四, 10/15/2020 - 15:09 提交

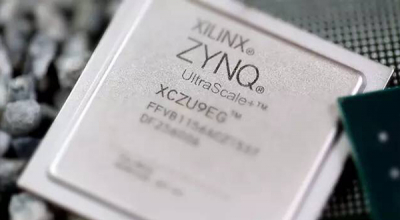

Integrated Block for PCIe® 核是高可靠性、高带宽、高可扩展性的串行互连构建块,适合与 UltraScale+™ 器件配合使用。该核可对 UltraScale+ 器件中提供的集成块进行例化。

Integrated Block for PCIe® 核是高可靠性、高带宽、高可扩展性的串行互连构建块,适合与 UltraScale+™ 器件配合使用。该核可对 UltraScale+ 器件中提供的集成块进行例化。

Vivado Vitis 2020.1无法在Ubuntu部分版本上安装的解决办法

三课联播 绝对干货!扫码报名,即刻学习,与专家实时互动。

今天想和大家一起聊聊FPGA的IO。先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮同学有的做ARM,有的做linux,很少有人做FPGA,当时学FPGA仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的FPGA之路。

您听说过 FINN 吗?没有?这个答案并不令人惊讶,因为这是一个用于探索基于 FPGA 的深层神经网络推断的实验框架的全新再实现,而且它现在仍是赛灵思研究实验室 的测试版。然而, 虽然还是测试版,它已经发布了 v0.4b(测试版),并且自从在 GitHub 上开源以来,受到了广泛关注。

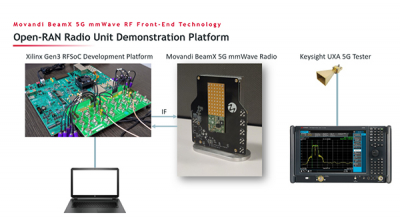

不久前举行的 BIG 5G 虚拟线上活动中,赛灵思与 Movandi 展示了双方在 Open-RAN(远端射频单元,即 RU)领域的合作。此举将继续推动开放式 5G 架构的发展与创新,最重要的是将加快其部署进程。

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

在数字相机往智能相机演进的过程中,芯片的算力需求也在快速地增长,成像从人看得舒服演进到机器看得清和看得懂,对视觉处理平台提出了更高的要求。因此我们特邀请到赛灵思系统架构师翁羽翔和深圳欧克曼技术(OCAM)的 CEO 吴志鹏先生一起与大家阐述基于赛灵思 MPSoC 的智能相机及边缘计算平台,以及欧克曼图像处理平台及相应解决方案。

有工程师反馈R5引导A53和R5的应用程序后,A53和R5的应用程序没有正确执行。因此做了一个MPSoC R5引导4个A53和两个R5的应用程序的例子。

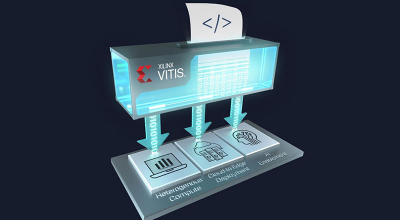

这是《创建 Vitis 加速平台》系列的第 2 篇博文。在前文中,我们讲解了如何创建硬件以及如何通过 XSA 将元数据 (metadata) 传递给 Vitis™。在本文中,我们将讲解如何使用此 XSA 以及如何创建在目标平台上实现设计加速所需的软件镜像。