【直播回放】如何使用PowerVR Toolkit加速您的应用程序?

移动设备上的图形应用越来越复杂和耗电,带来了广泛的挑战。能够使用工具来识别和修复这些问题可以节省开发人员大量的时间和精力。本次网络直播课介绍了在PowerVR上调试、分析和优化图形应用程序的过程。

移动设备上的图形应用越来越复杂和耗电,带来了广泛的挑战。能够使用工具来识别和修复这些问题可以节省开发人员大量的时间和精力。本次网络直播课介绍了在PowerVR上调试、分析和优化图形应用程序的过程。

通过本次网络研讨会,了解如何使用 Vitis AI 部署和运行您针对 Xilinx 嵌入式 SoC 和 Alveo 加速平台预先训练好的 DNN 模型。然后开始使用 Vitis AI 在板上运行示例。

本文描述如何从 Vivado® 高层次综合移植到 Vitis™ 高层次综合。

本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。

本次由信息技术新工科联盟主办,Xilinx、东南大学,西南交大联合承办的暑期学校已经在8月3日落下帷幕。从7月20日到8月3日这十五天间,超过1200名学员在全世界各地通过互联网参与了这一次暑期学校,累计了100小时的实践,超过10位讲师的精彩分享。

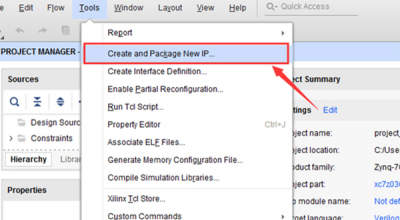

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过M_AXI接口对数据进行读取操作,此时设计一个基于AXI-Slave接口的IP进行数据传输操作就非常的方便

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

Vitis AI1.1 系列教程

Python是一种很棒的语言,语法简单,无需在代码中搜索分号。对于初学者来说,Python是入门最简单的语言之一。Python有大量的库支持,你还可以安装其他库来增加自己的编程经验。学了一阵子之后,你可能会觉得:为如此简单的操作写大量的代码有些令人困惑。