Xilinx的 MIG IP(非AXI4)接口时序以及控制

judy 在 周三, 06/17/2020 - 09:41 提交

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

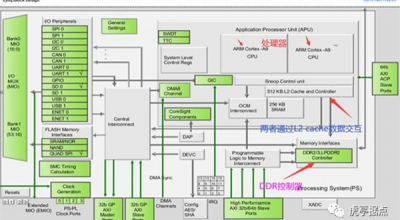

在ZYNQ的PS侧存在Cache,CPU与DDR之间通过Cache进行交互,数据暂存在Data cache中,在处理器对DDR进行写数据操作时,如果不将数据通过Cache送入DDR,DDR中的数据不会变化。在进行DMA操作时,如果没有对Cache进行适当的操作,可能导致以下两种错误

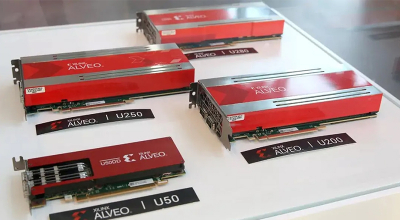

现在,企业和专业用户越来越意识到从物理和虚拟世界收集到的大量数据蕴含的价值。随着数据量继续呈指数级增长,对数据分析的需求也将以类似的速度增长。为此,数据中心必须加速转型,以达到增加网络带宽,优化人工智能等工作负载的目的

本文简要介绍了 ToF 传感器的工作方式。然后,本文将介绍 Digilent 的 Pmod ToF 板,并说明如何将其与 Digilent 的 Zybo Z7-20 开发板结合使用,以评估 ToF 技术并在自己的设计中快速部署光学距离感测。

本文演示了使用Vivado设计套件和Xilinx软件开发套件构建基于Zynq UltraScale + MPSoC处理器的嵌入式设计。提供有效的嵌入式系统设计的动手教程。

“以新发展理念为引领,以技术创新为驱动,以信息网络为基础,面向高质量发展需要,提供数字转型、智能升级、融合创新等服务的基础设施体系。”这便是的近来备受关注的新基建。按下快进键的新基建,也在推动着智慧安防、智慧交通和智慧城市等领域的快速发展。

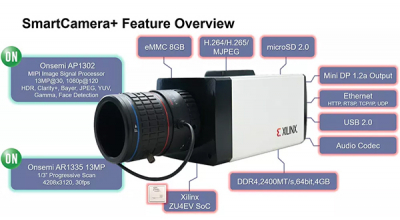

MPSoC EV 系列支持H.265编解码。在规格中,1080p编解码都可以达到8路1080p30,总体相当于1080p240。使用2018.3 VCU TRD 实际测试,性能更好。

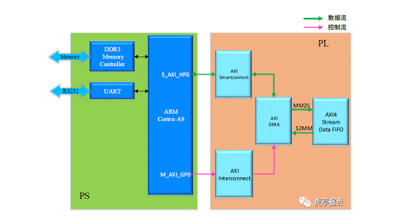

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码

数字频率调制是利用载波的频率传输信息的一种调制方式,FSK是在ASK之后出现的一种调制方式,抗衰落能力较强,在一些衰落信道中应用广泛。

PetaLinux是一个开发和构建环境,可自动执行许多任务,以完成在Zynq®-7000SoC和Xilinx®7系列FPGA上启动嵌入式Linux。本指南包含有关构成PetaLinux工具环境的各种工具的详细信息。