Vivado2018 中使用modelsim联合仿真

judy 在 周三, 06/10/2020 - 09:28 提交

vivado 中使用modelsim联合仿真

vivado 中使用modelsim联合仿真

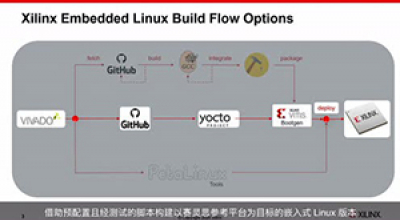

在本视频中我们将简单介绍 PetaLinux 工具开发与构建环境此环境支持客户构建以赛灵思器件为目标的 Linux 版本,并快速评估赛灵思嵌入式平台。

Block RAM与Distributed RAM,简称为BRAM与DRAM, 要搞清楚两者的区别首先要了解FPGA的结构: FPGA=CLB + IOB+Block RAM CLB。一个CLB中包含2个Slice、8位寄存器、多路选择器、进位链等。

PetaLinux 是一种嵌入式 Linux 软件开发套件 (SDK),主要用于赛灵思 FPGA 基片上系统设计。本指南提供有关使用PetaLinux工具的操作和参考信息。

由于开发板DIGILENT Genesys2 的开发手册中说明了自带的时钟IP核为差分时钟,所以研究了下Vivado中差分时钟的配置方法

有些应用中,需要降低Xilinx MPSoC的功耗。缺省设置中,R5/GPU都被使能。如果需要省电,可以在Vivado里关闭R5/GPU。步骤如下:

1. 选中 MPSoC IP,在右键菜单中选择Block Properties.

2. 在窗口Block Properties中,选择Properties.

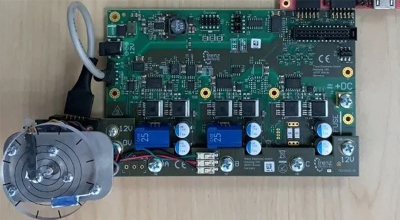

IIoT-SPYN是一个基于IIoT-EDDP开源平台和PYNQ软件框架的项目,它展示了如何在PYNQ开源框架下对电机进行控制、监视、捕获数据、可视化和分析。PL侧包含了对电机控制、状态采集的模块。在PYNQ中加载比特流后,就可以访问到这些已实现好的模块,对电机进行控制和状态检测。

振幅键控信号的解调主要有包络检波和同步检测两种方法,后者又被称为相干解调。相干解调需要提供与输入同频同相的载波信号,通常需要采用锁相环技术实现载波信号的提取,较为复杂,这里采用非相干解调的方法实现ASK解调,只需要将输入信号经过整流滤波即可得到基带信号。

本课程内容参考XILINX 官方文档PG046。这个IP支持Kintex®-7, Virtex®-7 FPGA GTX 和GTH 收发器,Artix®-7 FPGA GTX 收发器, Zynq®-7000 GTX and GTX收发器。Aurora 8B/10B IP core可以工作于单工或者全双工模式。IP CODE 的使用也非常简单,支持AMBA®总线的AXI4-Stream协议。

XAPP1247 是对应使用屏障镜像时的多重启动 (Multiboot) 和回退 (Fallback) 的示例应用。本篇博文提供了一种屏障定时器流程测试方法以及使用此方法时可能出现问题。