基于TCP/IP协议的电口通信

judy 在 周五, 06/05/2020 - 16:18 提交

LWIP可以通过硬核实现或者软核实现,具体要看FPGA的选型,其中硬核可以通过硬核自带的GMAC通过直连PHY或者EMIO扩展到PHY都可以实现相应功能,同时硬核也可以通过AXI总线与相应的IP相连然后再同外部PHY连接实现相应功能。这部分Xilinx官方提供详细的文档xapp1306-ps-pl-ethernet-performance-lwip和测试例程

LWIP可以通过硬核实现或者软核实现,具体要看FPGA的选型,其中硬核可以通过硬核自带的GMAC通过直连PHY或者EMIO扩展到PHY都可以实现相应功能,同时硬核也可以通过AXI总线与相应的IP相连然后再同外部PHY连接实现相应功能。这部分Xilinx官方提供详细的文档xapp1306-ps-pl-ethernet-performance-lwip和测试例程

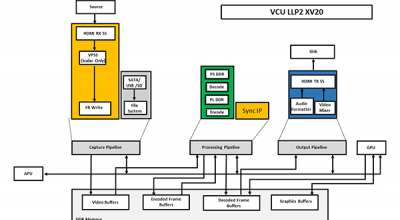

运行 Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display,可以测试HDMI输入输出,和VCU的低延时编码。Xilinx wiki的文章MPSoC VCU TRD 2019.2 - Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display以H.264和4K分辨率为例。

下面记录H.265和1080p分辨率的运行命令。

在VIVADO的实现的布局中,可以利用PBlock将某一个或某几个Cell(模块单元)固定在Device的固定区域上。如此,可以实现该模块内部的时序收敛,并且,该工具对于可重配置工具的使用也是必不可少的

赛灵思今日以线上会议形式举行了主题为“创‘新’正当‘适’”的大中华区核心市场中国媒体沟通会。在会上,赛灵思大中华区销售副总裁唐晓蕾阐述了赛灵思对数据作为“新基建”核心的洞察,分析了数据万有引力作用下,“新基建”七大核心领域从云到边缘智能计算的机遇与挑战,以及赛灵思所引领的自适应计算与“新基建”的完美契合和光明前景

2020年5月,赛灵思中国汽车市场联盟成员魔视智能(Motovis)宣布 A2 轮融资成功,融资金额高达一亿元人民币。资本市场的青睐,初创公司的激流勇进和脱颖而出,让我们再次把“自动驾驶距离我们到底有多远”的话题提上议程。

本期研讨会将通过一些设计实例来带您了解 Vitis 的主要特性,并掌握如何在 Alveo 加速卡上使用 Vitis 实现加速设计的流程;同时还将系统地介绍一下 Vitis 的主要设计资源。

适合哪些听众

在今年即将开幕的 LiveVideoStackCon 2020线上峰会上,作为自适应计算的引领者赛灵思再次受邀出席,并将为广大视频/图像处理从业人员带来全新的“构建自适应视频基础设施”的主题演讲。主题演讲将涵盖技术角度、经济角度的多项研究

疫情肆虐,全球经济全面遭受重创且持续低迷。然而,近日中国自动驾驶领域、嵌入式人工智能自动驾驶先锋企业魔视智能,Motovis (赛灵思在中国自动驾驶领域的重要合作伙伴之一),却逆势迎来 A2 轮融资成功的利好消息,融资金额高达一亿元人民币!

本文描述赛灵思 Alveo™ U200 和 U250 加速器卡的规格。

得益于人工智能的发展,它在机器人、物联网和智能个人助理(如Siri和Alexa)等方面创造了惊人的发展。那什么是人工智能呢?人工智能最简单的定义是:收集有关世界的数据,并利用这些数据进行短期和长期的预测。