【视频】如何在 Alveo 卡上快速使用 Vitis 进行开发

judy 在 周三, 03/18/2020 - 10:21 提交

本视频以 Alveo 加速卡为例,教您快速开始使用赛灵思 Vitis 开发软件进行开发。

本视频以 Alveo 加速卡为例,教您快速开始使用赛灵思 Vitis 开发软件进行开发。

软件工程师如何借助赛灵思统一软件平台Vitis将算法提速数倍?

如何快速打造从云到端可自适应的经得起时间检验的应用?

如何快速上手Vitis?

本案例利用PYNQ自定义Overlay驱动Respeaker,实现了一个智能音箱。ReSpeaker是一个四路ADC芯片AC108位转换芯片的四通道麦克风的设备,它支持I2S接口,在本案例中它需要连接到PYNQ-Z2的树莓派接口。

在本视频教程中,您将了解 Aveo 加速卡的 Vitis 基本流程,以及如何使用 Vitis 分析仪分析编译结果。

Vivado设计有工程和非工程两种模式:工程模式是使用Vivado Design Suite自动管理设计源文件、设计配置和结果,使用图形化Vivado集成设计环境(IDE)交互式处理设计。工程模式下,既可以通过图像界面下操作(GUI操作,鼠标操作),也可以通过运行Tcl脚本的方式在Vivado Tcl shell 中运行。

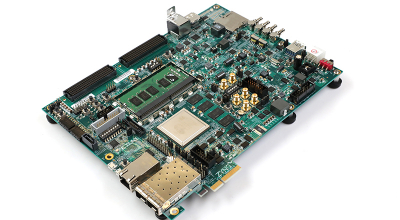

在前面的文章中ZCU106 XRT环境搭建【Xilinx Vitis】,已经生成了用于在Vitis的相关环境。Xilinx在GitHub分享了一个Vitis的应用程序加速开发的教程:2019.2 Vitis™ Application Acceleration Development Flow Tutorials

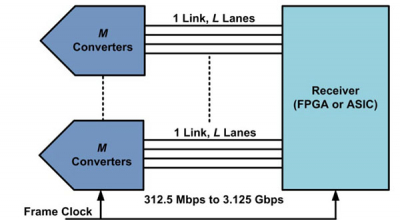

2006年4月,JESD204标准的最原始版本诞生,该标准描述了数据转换器(ADC或DAC)和接收器(FPGA或者ASIC)之间的吉比特串行数据传输链路(link)。在这个原始标准中,一个或多个数据转换器与接收器之间的串行链路被定义为有且只有一条数据通道(lane)

叮叮当铃儿响叮当

万众瞩目的 Versal Premium 正式亮相

先来看大家是如何评价它的 ↓

用机器视觉技术取代人工,可以提供生产效率和产品质量,因此机器视觉技术广泛应用于工业检测(机械零部件的尺寸和位置测量)、机器人视觉、人脸识别、车牌识别、自动光学检查、无人驾驶汽车、追踪定位等领域

如果您想开发面向最先进技术和协议的下一代最快速、最安全的网络,请跟随 Xilinx 高级产品线经理 Mike Thompson,了解 Versal ACAP 器件中的集成功能