ISE 2020: 当 8K 遇见 Xilinx 7nm Versal

demi 在 周五, 02/07/2020 - 11:07 提交

2月11-14日, 一年一度的欧洲专业视听集成设备与技术博览会 ISE 2020 将在荷兰阿姆斯特丹举行,赛灵思公司携业界首个 HDMI 2.1 FPGA 实现方案亮相 – 这是8K基于赛灵思最新赛灵思 7nm Versal AI Core 系列的首次方案演示。

2月11-14日, 一年一度的欧洲专业视听集成设备与技术博览会 ISE 2020 将在荷兰阿姆斯特丹举行,赛灵思公司携业界首个 HDMI 2.1 FPGA 实现方案亮相 – 这是8K基于赛灵思最新赛灵思 7nm Versal AI Core 系列的首次方案演示。

通过将特定于应用程序的配置数据(比特流)加载到内部存储器中,可以配置Xilinx®7系列FPGA。 7系列FPGA可以从外部非易失性存储设备加载自身,也可以由外部智能源(例如微处理器,DSP处理器,微控制器,PC或板载测试仪)进行配置。 在任何情况下,都有两个常规配置数据路径。

Verilog HDL是一种用于数字系统设计的语言。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。无论描述电路功能行为的模块或描述元器件或较大部件互联的模块都可以用Verilog语言来建立电路模型。Verilog模型可以是实际电路的不同级别的抽象。

现代ML算法不透明,易碎,并且容易受到数据中毒和篡改以及各种干扰的影响。 向在现实世界系统中部署AI的转变要求我们评估ML算法是否安全,强大和安全。 加入我们的行列,我们考虑这些问题可能如何对您的系统的性能和行为产生巨大和出乎意料的影响。

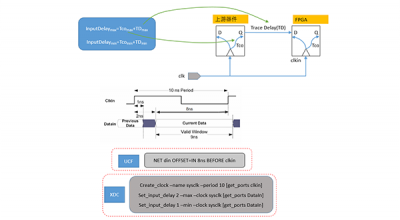

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

Xilinx的FPGA芯片中可以作为存储资源的包括LUT、BRAM、URAM。

很多FPGA初学者,都会怀疑学习FPGA有没有前途,发展前景怎么样,到底该怎样学习FPGA???各种迷茫,导致无法踏踏实实、全身心投入FPGA学习与开发工作中。下面请看看一个死磕FPGA 15年的大神给大家的肺腑之言,相信看完之后的你不在徘徊、不再犹豫、能够勇往直前。

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

赛灵思 Zynq® UltraScale+™ RFSoC 为要求最严苛的应用提供单器件 RF 转输出平台。更新的性能指标能够更加准确地衡量这些器件的直接 RF 采样功能。

十多年前,我们不会料到加速器在数据中心会这么流行。尽管它们并不普遍,但许多新的工作负载具备加速条件,并且移植工作使旧版应用程序可以卸载以提高性能。这种过渡在GPU上最为明显,但人们寄希望于FPGA将继续发展。