【下载】UltraScale架构GTH收发器

demi 在 周四, 01/02/2020 - 12:04 提交

Xilinx® UltraScale™架构是第一个ASIC级架构,可通过智能处理实现每秒数百吉比特的系统性能,同时有效地路由和处理片上数据。

Xilinx® UltraScale™架构是第一个ASIC级架构,可通过智能处理实现每秒数百吉比特的系统性能,同时有效地路由和处理片上数据。

AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少。

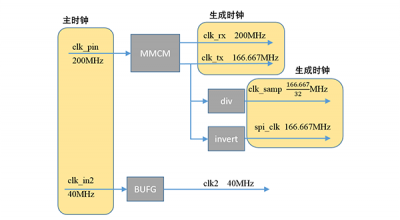

我们以Vivado自带的wave_gen工程为例,该工程的各个模块功能较为明确,如下图所示。为了引入异步时钟域,我们在此程序上由增加了另一个时钟--clkin2,该时钟产生脉冲信号pulse,samp_gen中在pulse为高时才产生信号。

本演讲视频将介绍从云到边缘的 Xilinx 全新统一 AI 平台。视频将涵盖通过剪枝器、量化器、编译器和运行时的基本工具流程,以直接从TensorFlow 等框架实现 AI 推断。

Xilinx的针对Gigabit应用的FPGA基本都会集成一些高速串行接口,统称为Gigabit Transceiver(GTx),包括GTP、GTR、GTX、GTH、GTZ、GTY(传输速率不断增加)等,不同系列的FPGA集成的GTx不同。

互联结构包括直通模式、只转换模式、N-1互联模式、N-M互联模式。

For 循环是解决问题的瑞士军刀,但是,当需要浏览代码以快速阅读你所做的事情时,它们可能会让人不知所措。有三种技术 — map、filter 和 reduce — 可以通过描述如何进行迭代来代替 for 训练。JavaScript 中也有这些技术,但是在 Python 中的实现略有不同。

所有市场的安全性都变得越来越重要。 在Zynq®UltraScale +™平台上使用受信任的执行环境(TEE),通过将安全关键元素与系统的其余部分隔离开来,可以提供主要的安全优势。

Verilog定位手段能够达到以下效果:方便FPGA版本定位、方便样品测试定位、防止他人将无法定位的故障推脱到自己身上。

在xdc文件中,按约束的先后顺序依次被执行,因此,针对同一个时钟的不同约束,只有最后一条约束生效。虽然执行顺序是从前到后,但优先级却不同;就像四则运算一样,+-x÷都是按照从左到右的顺序执行,但x÷的优先级比+-要高。