Xilinx FPGA常见配置模式总结

demi 在 周二, 09/24/2019 - 16:59 提交

Spartan6系列FPGA常见的配置模式有5种,由模式输入管脚M1、M0决定。该5种模式可分为3大类,1. JTAG模式(可归为从模式);2. 主模式;3. 从模式。

Spartan6系列FPGA常见的配置模式有5种,由模式输入管脚M1、M0决定。该5种模式可分为3大类,1. JTAG模式(可归为从模式);2. 主模式;3. 从模式。

在ZYNQ进阶之路3中我们讲解了PL端UART 发送的设计,本节我们讲解PL端实现串口UART的接收设计。

通过异构多处理、I / O 灵活性、基于硬件的确定性控制以及在网络安全、安全性和机器学习领域的全面解决方案,满足可扩展医疗保健平台不断增长的需求。

发起沿和捕获沿(Launch edge & Capture edge)

上一篇咱们介绍了7系列FPGA的整体时钟架构,知道了FPGA是由很多个时钟区域组成,时钟区域之间可以通过Clock Backbone 和CMT Backbone来统一工作。本篇咱们就说一下时钟区域的内部结构。

9月20日,米尔携手电子发烧友、电路城、面包板三大平台举办的MYD-C7Z010/20开发板试用活动正式上线啦!本次试用活动,是米尔回馈给各位电子工程师的重磅福利,只要您积极配合参与活动, 价值1450元 的MYD-C7Z010/20开发板试将免费赠送。

上周的PyCoder's Weekly上分享了一篇小文章,它里面提到的冷知识很有意思,作者稍作补充,分享给大家。它提到的部分问题,读者们可以先思考下:若两个元组相等,即 a==b 且 a is b,那么相同索引的元素(如a[0] 、b[0])是否必然相等?若两个对象的 hash 结果相等,即 hash(a) == hash(b),那么它们是否必然相等呢?

当您想到处理性能时,脑子里最先出现的影响因素往往并不是存储吧?但是,如果您正在处理大量的大型数据集,那么每个步骤的带宽都会影响到您完成工作的速度和效率。对于AI应用、8K视频处理、医疗成像、区块链和汽车解决方案等工作负载,高带宽性能带来的差异就如同玩具水枪与消防水带的区别。

FPGA在fintech领域的应用历史悠久,Virtex时代就可见高频交易的应用。FPGA由于其内部逻辑及计算单元的丰富性和灵活性,可定制低延时、高吞吐率的设计,基本上可以碾压软件实现的性能。

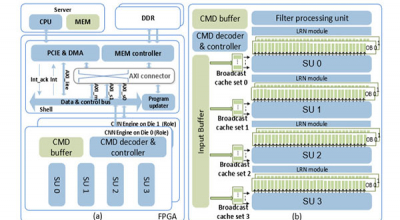

在本文中,我们开发了一个 FPGA 加速平台,该平台利用统一的framework架构,在数据中心实现通用卷积神经网络(CNN)推断加速。为了克服计算限制,4,096个DSP阵列用于不同类型卷积的超级单元(supertile units, SU),其在500MHz下提供高达4.2 TOP/s 16位定点性能。