硬件接口协议之“JTAG”

demi 在 周一, 09/02/2019 - 10:10 提交

本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

本文是关于Hot Chips 31大会观察与思考的系列文章的最后部分。在这一部分中,我想结合Philip Wong老师的Keynote,一起讨论一下集成电路制造工艺演进的问题,也想谈一下我自己关于制造工艺对于AI芯片创业企业的影响。

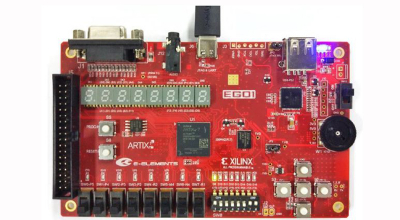

ZYNQ学习过程中一个重要环节是进行调试,当然在SDK中进行调试时,设置断点进行单步调试非常高效。但是ZYNQ中毕竟涉及到FPGA的硬件部分,于是如果可以通过UART与ZYNQ器件进行双向的通信会使得调试非常方便。

随着人们安防意识的不断增强和智能技术的持续发展,针对用户对安全系数高的智能电子锁的需求,使用FPGA蓝牙通信技术设计了基于FPGA蓝牙通信技术的智能电子锁系统。通过手机APP直接控制电子锁,对电子锁进行双重加密处理,具有开锁、修改密码,管理员控制用户开锁信息表,增添和删除能开锁的用户信息等功能。经测试,系统使用方便,动态灵活,安全可靠

axi_timer模块即为PS可以访问的PL计数器,通过计数值以及接入axi_timer的计数时钟周期,可以在PS内取得比较精确的计时。axi_timer有2种使用方式,一种是作为计数器使用,另一种是作为定时器使用

本文主要介绍I2C总线的读写操作流程。I2C总线的操作包括读和写,具体的操作流程如下:

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。报告时钟网络命令可以从以下位置运行:

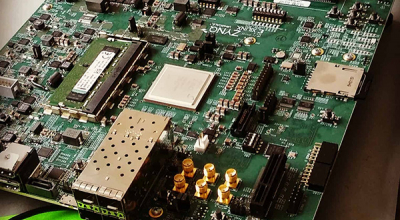

傲睿智存(Aupera Technologies)是数据中心视频处理系统领域的新兴企业。Aup2600 是 Aupera 提供的一种专用分布式视频处理系统,内置 48个赛灵思 Zynq® UltraScale+™ MPSoC。此外,Aup2600 还提供基于赛灵思 Vivado 环境的完整视频 +AI 软件框架和用于神经网络处理的深度学习处理器单元 (DPU)。

Zynq UltraScale+ MPSoC的PS有以下主要特点:一个四核64位ARM Cortex-A53处理器,带L1和L2级缓存和ECC功能,可单独上电和关电;Cache一致性互联单元为PS和PL提供双向Cache一致性保证;SMMU(系统内存管理)单元用于PS和PL虚拟内存管理;双核ARM Cortex-R5F处理器(带浮点扩展),可运行在锁步模式或独立工作模式

在业界,串口又称为通用异步收发器(Universal Asynchronous Receiver/Transmitter,简称UART),它的通信方式遵循一套串口协议:UART通信首先将接收到的并行数据换成串行数据来传输。数据帧从起始位开始,后面是7个或8个数据位,一个可用的奇偶校验位和一个或几个高位停止位