Zynq UltraScale+ RFSoC

judy 在 周三, 05/29/2019 - 14:06 提交

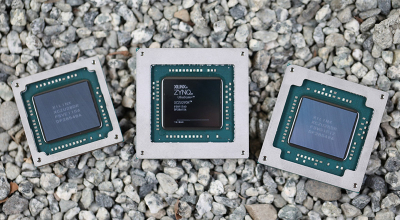

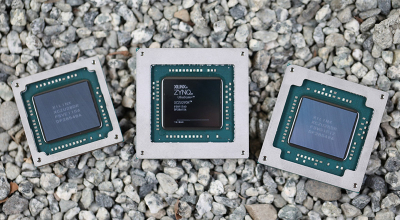

Zynq UltraScale+ RFSoC将业界唯一单芯片自适应射频平台扩展至全面支持 6GHz 以下频段,实现全面射频-模拟信号链突破性集成、软决策前向纠错 (FEC)以及适用于单芯片射频的完整的SoC,广泛的器件组合提供不同的直接RF性能,满足各种频谱需求和使用案例。

Zynq UltraScale+ RFSoC将业界唯一单芯片自适应射频平台扩展至全面支持 6GHz 以下频段,实现全面射频-模拟信号链突破性集成、软决策前向纠错 (FEC)以及适用于单芯片射频的完整的SoC,广泛的器件组合提供不同的直接RF性能,满足各种频谱需求和使用案例。

DNNDK是深鉴科技面向AI异构计算平台DPU自主研发的原创深度学习开发SDK,涵盖了深度神经网络Inference阶段的模型压缩(包括剪枝和定点化)、编译优化和高效运行时支持等各种功能需求,为DPU平台深度学习应用开发和部署提供高效全栈式解决方案。

DMA外设特点:

DMA引擎拥有一个灵活的指令设置DMA的传输;

拥有8个cache线,每一个cache线宽度是4个字;

拥有8个可以并行的DMA通道线程;

拥有8个中断给中断控制器;

拥有8个DMA触发事件并且可以编码控制;

128个(64bit)的MFIFO,在传输的时候读写端可写入到此FIFO;

支持任意内存到内存的传输;

说起xilinx的FPGA时钟结构,7系列FPGA的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如图1所示,理解了这张图,咱们就对7系列的FPGA时钟结构了如指掌,下面咱们就聊聊这张图

双核Zynq中共有20个PL到PS的中断。IRQF[15:0]是16个共享外设中断(SPI),可配选择上升沿触发或高电平触发,中断号为61-68和84-91。另外还有4个私有外设中断(PPI)IRQF2P[19:16],每个CPU都有一个来自PL的FIQ(快速中断)和IRQ,其中断敏感类型固定。

Image Matters 始终致力于为极端影像应用开发创新型高性能平台。ORIGAMI Module B20 是一款永不过时的视频制作解决方案,旨在为高级视频应用提供极端连接及处理功能,可为进行扩展、满足未来接口需求提供高度的灵活性。

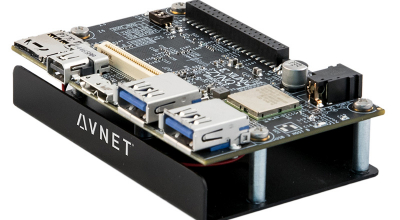

Ultra96™ 是一款基于 Arm 技术的赛灵思 Zynq UltraScale+™ MPSoC 开发板,符合 Linaro 96Boards 规范。96Board 是开放平台规范,为开发平台定义了一个标准电路板布局,可供软件应用程序、硬件设备、内核和其他系统软件开发人员使用

Xilinx 提供全面的硬件和软件解决方案,以实现 AI 推断。下图显示了高层次组件。

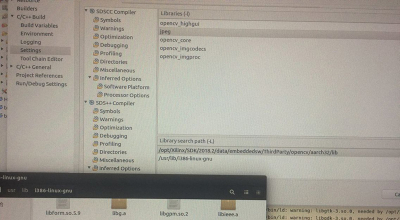

接着上一篇 http://xilinx.eetrend.com/blog/2019/100043298.html 上一篇末尾在Sdx中使用xfOpenCV出了一些问题。我是ubuntu16.04,Sdx2018.2。

本文安装环境为VM14.1.1 + ubuntu16.04_64 + petalinux_2017.4 ,流程按照ug1144(v2017.3)文档进行讲解。