Xilinx 为诊断和临床提供的医疗保健解决方案——机器人辅助手术

judy 在 周日, 05/05/2019 - 09:42 提交

机器人辅助手术是临床外科和医疗保健领域发展最快的项目之一。一些行业专家、临床医生和外科医生认为,机器人在手术中的应用是大势所趋,可实现切口更小、恢复时间短、住院时间缩短、并发症风险降低、失血和疼痛减少。如今,世界上不到 5%的手术使用机器人辅助,预计它将以惊人的速度增长

机器人辅助手术是临床外科和医疗保健领域发展最快的项目之一。一些行业专家、临床医生和外科医生认为,机器人在手术中的应用是大势所趋,可实现切口更小、恢复时间短、住院时间缩短、并发症风险降低、失血和疼痛减少。如今,世界上不到 5%的手术使用机器人辅助,预计它将以惊人的速度增长

Arduino 和 Raspberry Pi 开发板是颠覆嵌入式系统开发方式的登峰造极之作。从前,嵌入式系统的开发从硬件开始。项目步骤一般如下:

1. 规范系统要求,包括粗略估计处理速度和 I/O 要求。

2. 选择符合功率、性能和价格要求的适当微控制器或微处理器。

硬件描述语言(HDL)编码技术让您:

•描述数字逻辑电路中最常见的功能。

•充分利用Xilinx®器件的架构特性。

核磁共振成像 (MRI) 仪和计算机断层扫描 (CT) 仪是高度同步的大型机器,需要在其不同的子系统之间提供显著的计算能力。与 Xilinx Zynq UltraScale+ SoC 集成,可为梯度放大器中所需的高速 SiC 逆变器控制、RF 发射链所需的 RF 波形合成,以及 RF 接收所需的海量并行 ADC 接口及信号处理提供一个平台

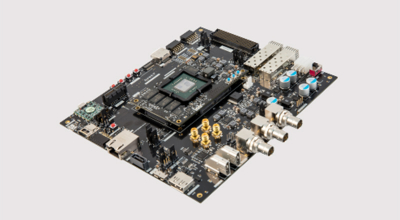

Zynq UltraScale+ RFSoC ZCU1275 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ XCZU29DR-2FFVF1760E RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。所有 16 个 12 位 2GSPS ADC、所有 16 个 14 位 6.4GSPS DAC、所有 16 个 GTY 收发器以及所有 4 个 GTR 收发器都可通过 Samtec BullsEye 连接器访问

Python字符串拼接的几种方法

过去,设计人员倾向于使用现场可编程门阵列 (FPGA) 在硬件设计中提升计算密集型应用的性能,例如计算机视觉、通信、工业嵌入式系统,以及越来越多的物联网 (IoT)。然而,传统 FPGA 编程中涉及的繁琐步骤一直让人望而却步,促使设计人员到目前都还在寻求替代处理解决方案。

为了能让工程师尽快掌握ZYNQ-7000 SoC的特性和优势以设计更智能更灵活的系统,提高产品竞争力和加速产品更新及上市进程,依元素科技推出为期2天的培训班。本培训课程主要介绍Zynq 架构的特性和优势,旨在为您设计 Zynq SoC 项目提供决策

在如今的超声波中,通道数直接转化至更高分辨率和深度—对于发现和识别问题而言二者皆是至关重要的因素就这些功能而言,Xilinx UltraScale™ + 系列将单位 DSP 逻辑单元比提升数倍,在单器件上实现更高的信号处理性能。高速串行收发器为连接兼容 JESD204B 的模拟前端组件提供了一个节能的高速接口

UltraZed-EV™ 入门套件包含 UltraZed-EV 系统级模块 (SOM) 和所绑定的载卡,可为基于 Xilinx 功能强大的 Zynq® UltraScale+™ MPSoC 器件系列完成系统原型设计和评估提供完整的系统