7 eries FPGAs SPI MultiBoot应用笔记(含资料)

judy 在 周四, 04/11/2019 - 09:43 提交

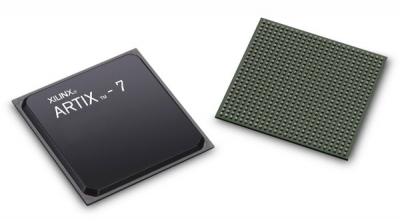

7 Series FPGAs MultiBoot功能指让FPGA从2个或者多个BIT文件中加载一个BIT文件运行程序,所以它的2个主要应用如下:

1. 更新新的BIT时,当更新失败或BIT出错会返回使用之前好的BIT运行程序;

2. 在多个已知好的BIT之间,通过外部触发来切换加载的BIT实现不同功能。

7 Series FPGAs MultiBoot功能指让FPGA从2个或者多个BIT文件中加载一个BIT文件运行程序,所以它的2个主要应用如下:

1. 更新新的BIT时,当更新失败或BIT出错会返回使用之前好的BIT运行程序;

2. 在多个已知好的BIT之间,通过外部触发来切换加载的BIT实现不同功能。

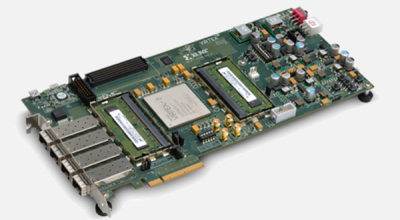

该演示将展示 4G 和 5G 如何在融合接入网络上与 CPRI 和 eCPRI/RoE(以太网无线电)传输共存,并将突出展示利用支持 IEEE 802.1CM 的时间敏感性网络为优化网络设计实现的受控时延。

Xilinx 资深 AI 方案技术专家张帆在赛灵思技术日上分享《用赛灵思 FPGA 加速机器学习推断》

最近使用Xilinx 7系列690T芯片的多个GTX接口传输千兆以太网数据帧时,在某些的测试情况下个别GTX接口会出现少量丢帧的问题,最后通过实验发现是时钟的分配使用问题,具体而言是GTX接口的QPLL和CPLL的使用问题。

针对当前无人机数据链日趋小型化,采用射频收发一体化设计,基于FPGA 对零中频射频收发器AD9361 进行配置,实现机载视频和遥控遥测的无线传输。测试结果表明,该设计可以实现无人机与地面站之间数据的可靠传输,同时满足小型无人机对数据链体积、重量、功耗和低成本的要求

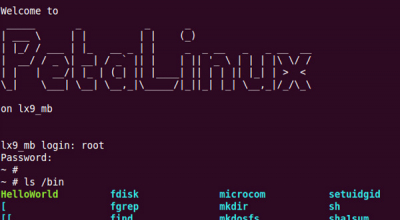

上一篇简单解释了Zynq配置的相关概念,本文将对Zynq-7000的软件开发进行简单介绍。如果设计者已经对ARM的开发方法很熟悉,上手Zynq的软件开发也会更快,相关概念理解起来也更快。

了解由阵列引起的性能限制,并学习一些优化技术来处理阵列以提升性能

在我之前接触的客户中,也只有少量公司在使用 Xilinx FPGA 和 SoC 芯片所提供的安全功能。其他的情况,可能是有物理环境能保证产品不被别人接触到;但更多可能是工程师觉得安全功能不是必须的,或者使用安全功能太复杂。攥写本文,我希望能让大家看到:

上电自复位对FPGA的稳定性及其重要,因为对于某些设计,上电之后需要进行一些状态寄存器的初始化,或者系统自己初始化都需要一个复位信号。在这里我就介绍一个比较好用的方法,大家一起学习一下

作者:OpenSLee,来源:FPGA开源工作室