时钟信号的几种设计方法

joycha 在 周二, 03/26/2019 - 14:55 提交

时钟信号是FPGA时序逻辑设计中必不可少的条件,一般情况下在FPGA始终资源充裕的情况下通常采用FPGA内部自带的内核生成时钟信号,例如DLL/MMC,但是一旦出现资源不够的情况,就只能另寻他法了

时钟信号是FPGA时序逻辑设计中必不可少的条件,一般情况下在FPGA始终资源充裕的情况下通常采用FPGA内部自带的内核生成时钟信号,例如DLL/MMC,但是一旦出现资源不够的情况,就只能另寻他法了

与 O-RAN 联盟成员 AT&T、Anokiwave、Ball Aerospace 和 Keysight 合作,实现了 O-RU 概念验证演示。

本课程向新老设计人员介绍了 UltraScale™ 器件架构的最新内容,包括介绍全新CLB资源、时钟管理资源(MMCM 和 PLL)、全局和区域时钟资源、存储和DSP资源、源同步资源及IO接口模块特性。 同时,也阐述了如何将原有设计移植到最新UltraScale器件架构上

Xilinx 大中华区业务拓展总监朱勇在Xilinx技术日上分享《无与伦比的并行处理—FPGA加速度基石》

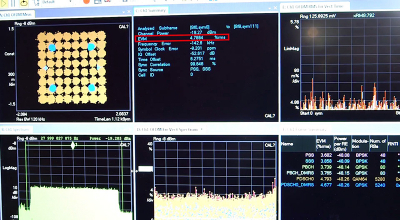

Xilinx FPGA器件内部有专用的硬件资源,支持大量设计时钟的使用。通常板子上有一个外部组件(如有源晶振)产生时钟信号,通过输入端口进入器件内部。外部时钟可以通过MMCM、PLL、BUFR等特殊原语生成其它时钟,也可以由LUT、寄存器等常规单元进行转换(通常称作门控时钟)。本文将讲述如何根据应用情况定义时钟

FPGA设计的特点是需要不断不断的迭代各个设计流程来达到最终的设计,同时迭代的成本大,它比单片机开发更注重迭代的开发思想。所以,设计的前期一定要从系统的角度考虑好系统的方案,然后在系统这个方案中不断的迭代,不然后期发现由于系统方案的问题就得不偿失了,好的系统架构就是成功一大半了

该演示结合单个 PON 硬件,允许 1G 至 25G PON 进行软件更新。这些 PON 解决方案以正确的成本结构将适当的应用定为目标。此外,该演示还将针对开放式架构展示 VOLTHA 集成。

3月19日,备受瞩目的Xilinx技术日在上海龙之梦万丽酒店隆重举办!此次活动由全球最大的可编程芯片厂商Xilinx主办,邀请行业最顶尖的FPGA专家和企业汇聚一堂,集思广益,分享和交流FPGA产品开发经验与应用方案!作为Xilinx在中国智能汽车电子领域唯一的Certified member,深圳市自行科技有限公司受邀参加,并携公司高性能前装量产DMS与ADAS等产品亮相

在ZYNQ SOC 入门基础(二)MIO 实验中讲解了MIO的使用,本节就来讲一下EMIO的使用。在实上一章中对ZYNQ的GPIO做了简单的介绍,ZYNQ的GPIO有(multiuse I/O)MIO和(extendable multiuse I/O) EMIO。

InfiNet 是长距离、点对点和点对多点网络通信领域的无线行业领导者,致力于使用 Xilinx Zynq SoC 加速其运行在 3、5 和 6 GHz 范围的网络回程产品的上市时间。Xilinx 还为 InfiNet 提供了部署其软件定义无线电的灵活性,以跟上快速发展的电信业务