System Generator从入门到放弃(二)——Digital Filter

judy 在 周四, 12/27/2018 - 16:34 提交

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

本篇主要介绍PCIe总线的AC耦合电容、总线的去加重等高速信号调整技术。

本设计咨询主要介绍一个错误的时钟偏移计算导致错误时序收敛的问题。

本文为在FPGA中支持DSR协议的路由表项管理功能,设计一种基于有限状态机[8]的实现方法。本文的设计中,状态机包含一个初始状态和3个功能状态。有限状态机的3个功能状态一起联合实现路由存储、路由查找、路由删除的功能。有限状态机使得硬件代码符合时序电路的风格

Zynq系列FPGA分为PS部分和PL部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分,实质是直接操作arm9内核的处理器。

这次先是最简单地在PL部分编写一个流水灯实验的代码。

使用的开发环境是vivado 2016.4。

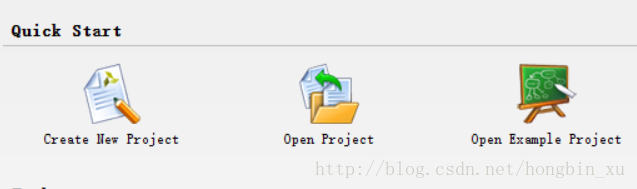

1、新建工程,Create New Project。

2、next。

3、选择工程目录,和输入工程名字。

本视频将向您介绍赛灵思 Alveo U200 和 U250 自适应加速卡,包括硬件规格、板卡安装、软件安装包下载与安装、板卡验证等内容,助您快速开始加速计算之旅

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

VCU128 开发板采用全新 Xilinx VU37P HBM FPGA,利用堆叠芯片互连将 HBM 裸片添加到封装基板上的 FPGA 裸片旁边。支持高带宽存储器(HBM) 的 Xilinx FPGA 是计算带宽问题(与在 PCB 上使用 DDR4 等并行内存相关)的最优解决方案

赛灵思业经验证的 5G 网络解决方案以及丰富的生态系统可以加速前瞻性的 5G NR 网络的部署和管理,包括智能网络遥测, AI/ML 工具, SoN 等,同时还可实现网络的无缝升级,从而满足那些新兴的标准和算法的更迭。我们诚挚地邀请您光临赛灵思在 2019 年世界通信移动大会(MWC 2019)上的展位,体验赛灵思的芯片、IP 和工具如何帮助客户打造灵活应变、智能、领先的 5G 系统