Vivado使用指南(一):如何在Vivado中添加自己喜爱的文本编辑器

judy 在 周二, 12/11/2018 - 17:26 提交

一、如何在Vivado(2017.2)中添加自己喜爱的文本编辑器。

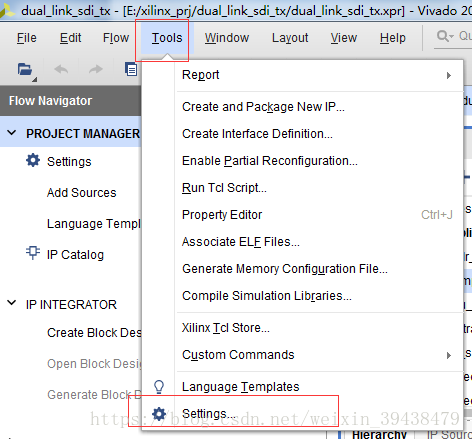

1、打开Vivado软件,选择Tools-->Settings。

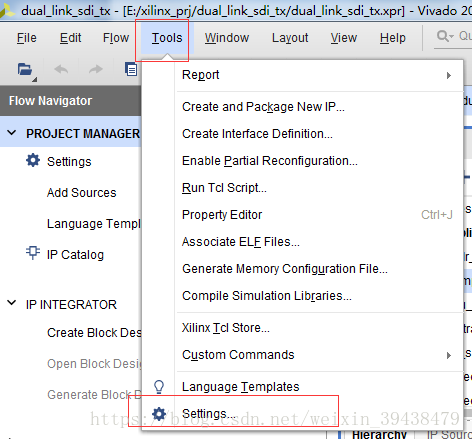

2、在弹出的界面中选择Text Editor-->Custom Editor。

3、在Editor:框中输入你想要添加的文本编辑器的路径。注意:后面需添加[file name] -[line number]。

一、如何在Vivado(2017.2)中添加自己喜爱的文本编辑器。

1、打开Vivado软件,选择Tools-->Settings。

2、在弹出的界面中选择Text Editor-->Custom Editor。

3、在Editor:框中输入你想要添加的文本编辑器的路径。注意:后面需添加[file name] -[line number]。

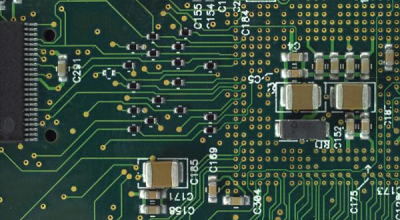

本篇主要介绍逻辑互连中的AC耦合电容。

1、AC耦合电容的作用

2、AC耦合电容的位置及大小

Maxeler 在 Xilinx Alveo 加速卡上展示实时风险

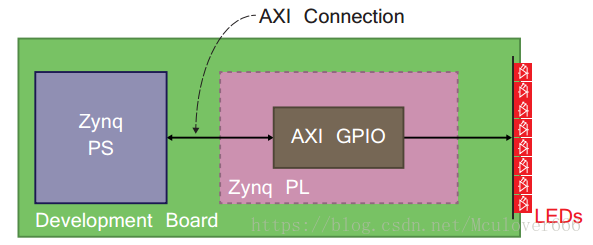

上一节中分别独立实验了Zynq的PS端和PL端,并初步实验了PS端先硬件再软件的开发流程和IP核设计的设计方法。第一节中提及到:Zynq是以PS端的ARM处理器系统为核心的,PS端和PL端是通过AXI总线,并且Xilinx已经提供了各种AXI通信的IP核,接下来的实验中将会更加明确的体验到利用IP核设计的设计方法。

1.实验目标

板载的LED和RGBLED都是接在PL端的,这个实验将利用PS端程序通过AXI总线控制连接在PL端的LED。

2.实验步骤

整个实验流程参考《The Zynq Book Tutorials》的chpt1:First Designs on Zynq(这本实验指导手册是英文的,但我个人认为英文原版要比中文看着清楚很多)。

FPGA设计的时候,我们需要考虑功耗,功耗自然与温度相关,还需要考虑电源供电电压的稳定性以满足高低温的环境,有没有考虑过,怎么监控FPGA内部的温度和电压变化情况,这对项目的优化和评估用处很大

作者:廖海鹏,卿粼波,滕奇志,何小海,邓媛媛,来源:2018年电子技术应用第12期

文章是对官方文档Resource Manger部分的总结,写得不是很有条理,仅是自己对这部分学习认识的一个总结,希望对看到的人有所帮助。

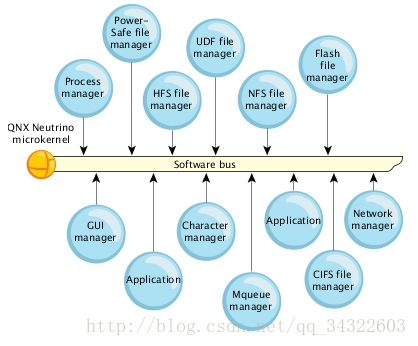

QNX OS是微内核操作系统,其内核仅仅提供进程调度、进程通讯等服务。文件访问、设备驱动等服务都属于用户空间的任务,下图是QNX系统的架构图

除了内核外其它所有进程都属于用户空间,内核作为一个软件总线,将其它所有资源互相连接起来,这种结构看起来像一个团队而不是层次结构,几个相同等级的“player”通过内核相互协调完成任务。

总的来看,资源管理器就是一个在文件系统名称空间中注册了一个名称的进程。其它进程使用其路径来与资源管理器通信。

资源管理器通常用来向各种各样类型的设备提供接口,涉及到管理实际的硬件设备。在其它操作系统这个功能作用通常归为设备驱动。但在QNX系统中,资源管理器不像是设备驱动,它是从内核中剥离出来,看起来就像其它用户级程序一样。若我们需要针对自己的板卡驱动硬件,这个驱动程序的开发就是资源管理器的开发。

视频简要描述了 Alveo U200 和 U250 灵活应变加速器卡,并逐步介绍了硬件和软件安装步骤,包括下载安装包以验证开发板和软件安装。

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。

下面详细介绍第二部分:不同逻辑电平之间的互连。

1、LVPECL的互连

1.1、LVPECL到CML的连接

作者:Mculover666

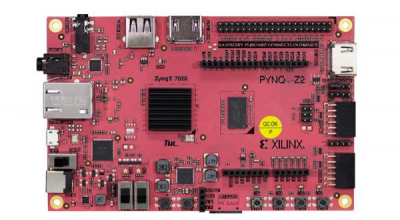

在上一篇中提到,Pynq是为了降低开发人员的门槛,但是作为一个学习嵌入式开发的学生,当然要一步一个脚印打好基础,所以选择从Zynq入手学习,等跑起来Linux系统再运用Python开发也不迟,知其然也知其所以然,开发效率更高,所以接下来的几篇都是关于Zynq的,如果想直接玩Pynq可直接跳过,毫无影响。

1.Zynq的架构

在开始实验之前对Zynq芯片有一个基本的认识,如果想深入了解关于Zynq的理论部分,推荐参考The Zynq Book,有英文版和中文版,在此对于Zynq的理论浅尝辄止,不做深究,重点放在实验应用上。

Zynq中包含两大功能块:PS部分和PL部分。