Zedboard学习(四):PS+PL搭建SoC最小系统

judy 在 周二, 01/15/2019 - 14:06 提交

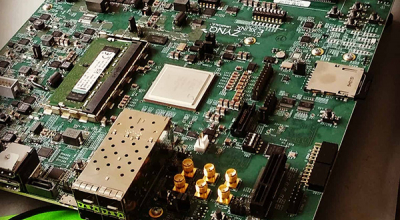

Zynq最核心的设计理念就是软件加硬件,即PS+PL。通过软硬件协同设计,结合了FPGA与双arm9内核,对于嵌入式拥有极大的优势。整个片上系统主要使用资源:ZYNQ系列FPGA XC7Z020、2片DDR、串口芯片(USB转UART)。Zedboard板子自带了这些资源,不需要另外添加模块。

Zynq最核心的设计理念就是软件加硬件,即PS+PL。通过软硬件协同设计,结合了FPGA与双arm9内核,对于嵌入式拥有极大的优势。整个片上系统主要使用资源:ZYNQ系列FPGA XC7Z020、2片DDR、串口芯片(USB转UART)。Zedboard板子自带了这些资源,不需要另外添加模块。

神经网络(NN)几乎可以在每个领域帮助我们用创造性的方式解决问题。本文将介绍神经网络的相关知识。读后你将对神经网络有个大概了解,它是如何工作的?如何创建神经网络?

本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

本视频将向您详细介绍 SDAccel 中可供调用的硬件调试选项,以及如何使用这些选项。另外还将通过实例操作向您演示在硬件上如何运行调试内核接口。

Python是一门简单易学的编程语言,语法简洁而清晰,并且拥有丰富和强大的类库。与其它大多数程序设计语言使用大括号不一样 ,它使用缩进来定义语句块。在平时的工作中,Python开发者很容易犯一些小错误,这些错误都很容易避免,本文总结了Python开发者最容易犯的10个错误,一起来看下,不知你中枪了没有。

本PPT介绍了使用 SDAccel 进行主机及加速器代码优化。

全球机器视觉市场仍然处在一个稳健快速的成长阶段。根据BCC Research的预测,2018年全球机器视觉市场约为160亿美元,到2023年市场规模将增长至248亿美元,年复合增长率为9.2%。这个增长速度看上去似乎并不算抢眼,但要知道这个市场从2002年开始一直保持着年均两位数的增长,由此你就可以看出其背后强劲的动力了。

赛灵思诚挚邀请您访问我们的展位,观看赛灵思汽车级解决方案的现场演示;体验低功耗、低时延及高吞吐量下无与伦比的性能;并与专家探讨灵活应变而且智能的未来汽车

在2018年10月举办的赛灵思开发者大会 (XDF)上,公布了有关赛灵思创新产品 Zynq® UltraScale+™ RFSoC 的几个值得关注的更新。以下是为错过论坛的人总结的几个亮点。

当我和人们谈起FPGA时,我听到很多人说:“我不知道它们的工作原理”、“它们太复杂了”、“我无法用C语言编程”。我不希望看到这样一种神奇的器件遭受如此冷遇,因此下面我将尝试解答一些常见问题