【Xilinx 技术日上海站】FPGA –云计算时代的头等公民

judy 在 周三, 03/13/2019 - 09:43 提交

赛灵思技术日活动(Xilinx Technology Day)上海站即将拉开帷幕,六大重磅主题演讲人及嘉宾,将为与会者带来FPGA 行业趋势及赛灵思最新产品及技术动态最专业、最精准的分享。

赛灵思技术日活动(Xilinx Technology Day)上海站即将拉开帷幕,六大重磅主题演讲人及嘉宾,将为与会者带来FPGA 行业趋势及赛灵思最新产品及技术动态最专业、最精准的分享。

2019年3月21日,赛灵思大中华区销售副总裁唐晓蕾将应邀出席2019 AI 芯片技术论坛,并发布题为“Xilinx 自适应平台 – 全方位创新的基石”的主题演讲。同时,她还将出席该会议当天的高端对话环节,就人工智能领域普遍关注的人工智能创新及赛灵思灵活应变的平台解决方案分享观点和见解

重定时(Retiming)是一种时序优化技术,用在不影响电路输入/输出行为的情况下跨组合逻辑寄存器从而提高设计性能。图1所示的电路是六输入加法器,其中有一条关键路径,红色推出显示的路径是限制整个电路性能的关键路径。

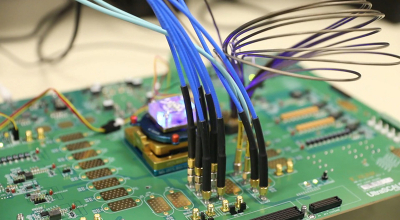

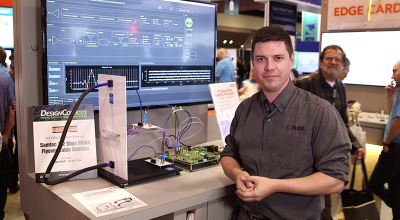

在 DesignCon 2019 上,Xilinx 和 Molex 展示了一组演示。 首先,Virtex UltraScale + FPGA 中的 Xilinx GTM 58G PAM4 SERDES 运行于超过 3 米的 QSFP-DD 直接连接铜缆,由Molex Near-Stack 高速连接解决方案提供支持。

在使用Python多年以后,我偶然发现了一些我们过去不知道的功能和特性。一些可以说是非常有用,但却没有充分利用。考虑到这一点,我编辑了一些你应该了解的Python功能特色。

设计约束就是定义编译过程中必须满足的需求,只有这样才能保证在板子上工作时功能正确。但不是全部约束在所有过程中都会使用,比如物理约束只用在布局和布线过程中。Vivado工具的综合和实现算法时时序驱动型的,因此必须创建合适的时序约束。我们必须根据应用需求选择合理的约束,过度约束或约束不足都会造成问题

云服务和5G的推出推动了数据流量的大幅增长,这为满足网络日益增长的带宽要求带来了挑战,路由器和交换机接线端口密度、光学标准的扩展以及光纤网络带宽的更新是成本能够满足带宽需求的主要制约因素,转换为58G收发器是非常重要的一步,在相同的条件下它能够实现400G以上的数据传输速率

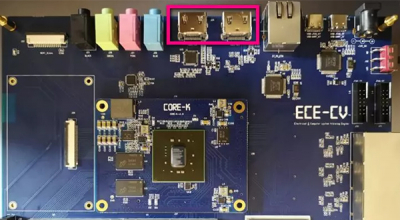

HDMI高清多媒体界面(英语:High Definition Multimedia Interface)是一种全数字化视频和声音发送接口,可以发送未压缩的音频及视频信号。HDMI可用于机顶盒、DVD播放机、个人计算机、电视游乐器、综合扩大机、数字音响与电视机等设备。HDMI可以同时发送音频和视频信号,由于音频和视频信号采用同一条线材,大大简化系统线路的安装难度

Xilinx 与 Deephi Tech 的机器学习战略

在 DesignCon 2019 上,Xilinx 和 Samtec 现场展示了 112G 有线背板。 该视频通过由下一代 Xilinx 112G PAM4 测试器件和 Samtec NovaRay 承载数据电缆组件生成、接收和验证的 112G PAM4 信号,显示了真实的背板长度,其传输速率是传统 PCB 互连无法比拟的。