软件无线电(SDR)的硬件架构

judy 在 周一, 06/17/2024 - 09:29 提交

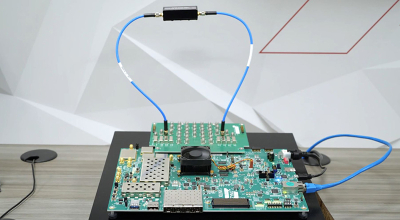

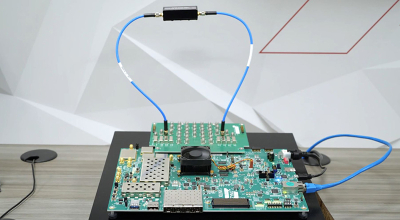

ZYNQ+AD9361是一种基于Xilinx Zynq FPGA和ADI公司的AD9361 RF捷变收发器的开源SDR硬件平台。

ZYNQ+AD9361是一种基于Xilinx Zynq FPGA和ADI公司的AD9361 RF捷变收发器的开源SDR硬件平台。

本文将从基础概念入手,逐步深入到AXI DataMover IP的配置和使用,帮助读者快速掌握这一强大的IP核。

在使用Synplify综合时,此工具会自动优化我的设计。

下面我们先简单看下RISC-V的发展,然后再分析一下这些FPGA厂商为什么选择RISC-V。

逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。

很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗?

本文通过以LCD1602液晶显示模块为基础,介绍FPGA驱动LCD1602原理,详细介绍硬件原理图设计及FPGA驱动LCD1602软件设计

本文将详细探讨Latch的概念、产生原因、潜在危害以及如何避免Latch的产生。

在RGMII接口的设计中,除了上述2个方面外,还有一个重要的方面就是接口的时钟和复位方案。为什么会有这个问题呢?

下面以AMD-Xilinx 7系列FPGA为例,一步一步搭建一个HDMI输入DEMO