JESD204接口调试总结——Xilinx JESD204B IP AXI寄存器简介

judy 在 周三, 09/14/2022 - 09:24 提交

一般来说,如果在IPcore配置正确的话,不太需要通过AXI指令来进行参数的修改,不过如果能够支持AXI指令

一般来说,如果在IPcore配置正确的话,不太需要通过AXI指令来进行参数的修改,不过如果能够支持AXI指令

在对工程进行综合时,出现综合过程中出现中止或者完全不启动综合,类似下图,明明点击综合启动了几分钟

LUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!

服务器报告硬盘没有空间。执行脚本peta-del-build-temp.sh

什么是MMU?MMU是Memory Management Unit的缩写,这原本是软件内存管理方面的一个概念

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

无论是FPGA还是ASIC的开发者,都或多或少地做过代码检视(code review)。

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

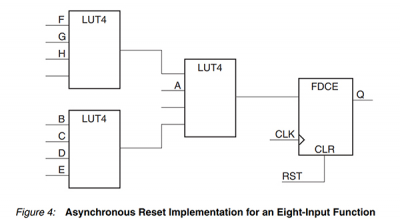

实现FPGA 设计最大性能化的一个重要因素是正确的RTL 编码设计。

今天我们就来详细分析一下,这个约束应该如何使用。