Xilinx SD-FEC硬核在5G-NR中的使用方法

judy 在 周二, 01/18/2022 - 09:30 提交

本文主要描述如何应用Xilinx的SD-FEC集成块硬核资源,进行5G-NR 通信系统PDSCH和PUSCH信道编解码开发。主要从SD-FEC集成块硬核特性、配置流程和注意事项等进行说明。

本文主要描述如何应用Xilinx的SD-FEC集成块硬核资源,进行5G-NR 通信系统PDSCH和PUSCH信道编解码开发。主要从SD-FEC集成块硬核特性、配置流程和注意事项等进行说明。

Xilinx的原语OSERDESE2是一种专用的并-串转换器,每个OSERDESE2模块都包括一个专用串行化程序用于数据和3状态控制。数据和3状态序列化程序都可以工作在SDR和DDR模式。

在FPGA设计中,我们经常需要用寄存器来寄存某些“数量类”的变量,比如FIFO的深度啦、或者计数器的最大值啦;又或者输入输出信号也需要将位宽用parameter参数化以便更好的调用等。

一个完整的通信系统,是十分庞大的,没有几百上千人,在短时间内是做不好的。本文仅仅针对5G NR中的基带算法部分,做一个简单梳理。

本系列文章基于xilinx三速以太网IP进行学习介绍。本文重点对以太网帧结构进行介绍。

大家都知道FPGA这玩意是老美搞出来的,所以很多术语都是翻译自英语。接下来就看几个在日常的技术文档中常见的拼写错误吧。

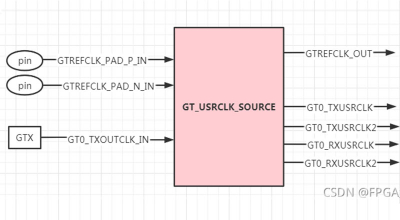

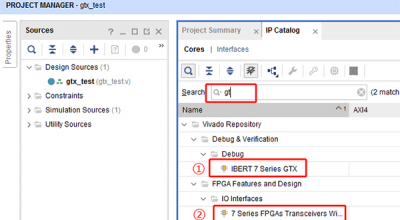

理解一个IP的用法,最好的办法就是打开官方的Example Design。 所以本文首先介绍Example Design,然后再替换成我们自己的收发测试模块,对比印证学习,差不多就能勉强把GTX给玩起来了。

首先回想一下,在平常的设计中我们是不是经常采用同步复位或者异步复位的写法,这一写法似乎都已经形成了肌肉记忆----每次我们写always块的时候总是会对所有的寄存器写一个复位赋初值的语句。

作为一名初学者,也曾被GTX一堆信号搞得头晕脑胀,在学习了各位大佬的文章后,结合自己的理解和实践,整理这一系列快速上手的GTX使用教程。

IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。