System Generator从入门到放弃(一)-安装与使用

judy 在 周二, 12/25/2018 - 09:05 提交

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲

在写资源管理器的时候,一般会用到处理close()来进行一些收尾工作,比如释放内存等等,查看QNX代码resmgr_io_funcs_t结构体对close()的处理有两个相关函数

程序的格式框架

下面是一段温度转换的代码示例:

#TempConvert.py

TempStr = input("请输入带有符号的温度值:")

if TempStr[-1] in['F','f']:

C = (eval(TempStr[0:-1]) - 32)/1.8

print("转换后的温度是{:.2f}F".format(F))

elif TempStr[-1] in['C','c']:

F = 1.8*eval(TempStr[0:-1]) + 32

print("转换后的温度是{:.2f}F".format(F))

else:

print("输入格式错误")

代码高亮是变成的色彩辅助体系,不是语法要求,可以检查基本语法拼写错误

首先,需要的肯定是Ubuntu操作系统。可以在自己的电脑上安装物理机,也可以是虚拟机下运行的。我的是在Vmware下运行的Ubuntu14.04 32位操作系统。由于zedboard上的Linux操作系统跑的是32位的,为了省去麻烦,我没有安装64位的

前面我们介绍过EMIO,但是不详细。MIO是PS的IO接口,这个M代表的是Multiuse,也就是多用途,在下图中我们可以看到54个MIO连接这么多东西,必须得复用,所以当我们开发的时候需要的功能配置上,不需要的去掉,防止IO口被占用

在调试Vivado 过程中,由于生成的BIT文件过大,而我使用的FLASH又是32MBIT的,出现了FLASH过小,无法烧录的情况。网上搜索到的方法都是说“generate progamming file下会有一个属性,进去了在-g compress后面打勾”,但是我使用的是VIVADO2017.2,该版本根本找不到这个选项。于是只能自己慢慢摸索,终于,找到了两种方法

在ZedBoard上开发基于QNX操作系统PL部分UART设备驱动的过程中遇到了一点问题,问题原因不明但总结下来给大家提供参考,也以便以后对QNX的进一步了解后回顾这些问题。

在前面几期的学习中,我们对于PYNQ的环境配置做了较为详细的介绍,并对PYNQ与ZYNQ的异同点做了较为深入的探究。我们知道,PYNQ = Python + ZYNQ,即将ZYNQ部分功能的Python化,直接调用Python库和FPGA硬件库进行功能的开发,典型的例子便是PYNQ_z2开发板

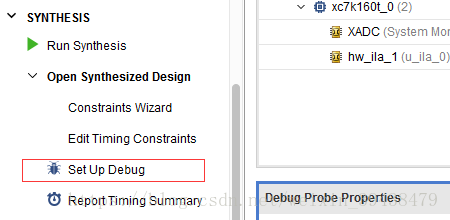

一、在想要抓取的信号之前添加(* mark_debug = "true" *)、保存、编译。如:

二、编译完成之后点击set up debug。

点击下一步.....

直至出现如下页面