面试题:三分频电路设计

judy 在 周一, 12/25/2023 - 09:34 提交

最近有人私信问了一个问题,如何设计占空比为50%的三分频电路

最近有人私信问了一个问题,如何设计占空比为50%的三分频电路

在FPGA设计中,几乎没人会主动使用锁存器Latch

本文介绍如何使用BRAM实现图像行缓存的设计

我们先看UG949中举的例子:时序场景如下图所示

本文将详细介绍使用FIFO来实现图像行缓存的设计

图像直方图用作数字图像中色调分布的图形表示。它绘制了每个色调值的像素数

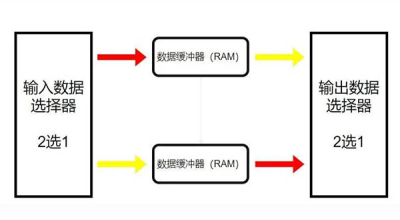

本文将详细介绍乒乓操作的基本原理、应用场景以及与FIFO的区别。

本文介绍多参考设计软件的语言模板

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑

今天介绍一下Cordic算法和Xilinx的Cordic IP。