Vivado使用指南(二):如何使用Vivado在线逻辑分析仪

judy 在 周四, 12/13/2018 - 10:19 提交

一、在想要抓取的信号之前添加(* mark_debug = "true" *)、保存、编译。如:

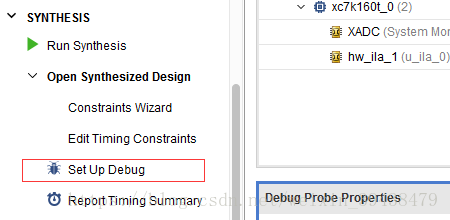

二、编译完成之后点击set up debug。

点击下一步.....

直至出现如下页面

一、在想要抓取的信号之前添加(* mark_debug = "true" *)、保存、编译。如:

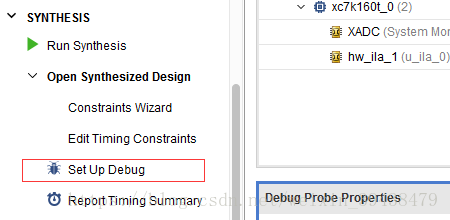

二、编译完成之后点击set up debug。

点击下一步.....

直至出现如下页面

在ZYNQ中,EMIO标号紧随MIO(0:53)之后,我定义了8个EMIO,采用标号54:61。在PS MIO Configuration中启用GPIO MIO 勾选EMIO GPIO(Width)选项,并设置宽度为8,即设置EMIO输出到8个PL的GPIO。具体程序如下:

一、如何在Vivado(2017.2)中添加自己喜爱的文本编辑器。

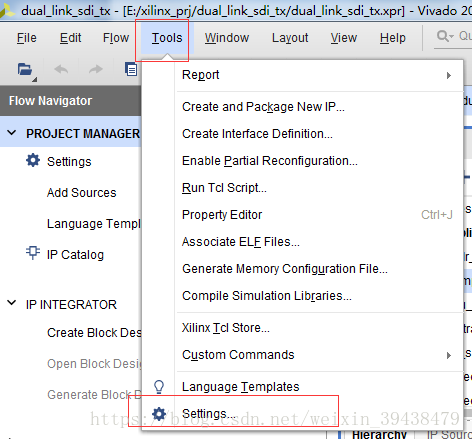

1、打开Vivado软件,选择Tools-->Settings。

2、在弹出的界面中选择Text Editor-->Custom Editor。

3、在Editor:框中输入你想要添加的文本编辑器的路径。注意:后面需添加[file name] -[line number]。

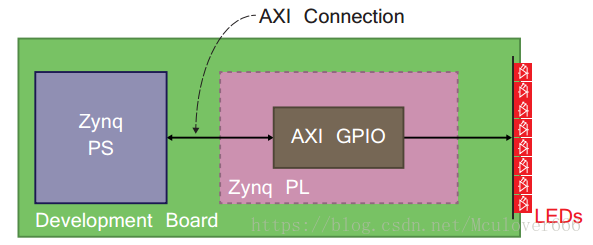

上一节中分别独立实验了Zynq的PS端和PL端,并初步实验了PS端先硬件再软件的开发流程和IP核设计的设计方法。第一节中提及到:Zynq是以PS端的ARM处理器系统为核心的,PS端和PL端是通过AXI总线,并且Xilinx已经提供了各种AXI通信的IP核,接下来的实验中将会更加明确的体验到利用IP核设计的设计方法。

1.实验目标

板载的LED和RGBLED都是接在PL端的,这个实验将利用PS端程序通过AXI总线控制连接在PL端的LED。

2.实验步骤

整个实验流程参考《The Zynq Book Tutorials》的chpt1:First Designs on Zynq(这本实验指导手册是英文的,但我个人认为英文原版要比中文看着清楚很多)。

作者:Mculover666

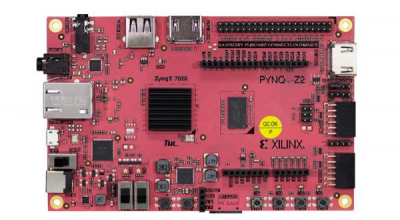

在上一篇中提到,Pynq是为了降低开发人员的门槛,但是作为一个学习嵌入式开发的学生,当然要一步一个脚印打好基础,所以选择从Zynq入手学习,等跑起来Linux系统再运用Python开发也不迟,知其然也知其所以然,开发效率更高,所以接下来的几篇都是关于Zynq的,如果想直接玩Pynq可直接跳过,毫无影响。

1.Zynq的架构

在开始实验之前对Zynq芯片有一个基本的认识,如果想深入了解关于Zynq的理论部分,推荐参考The Zynq Book,有英文版和中文版,在此对于Zynq的理论浅尝辄止,不做深究,重点放在实验应用上。

Zynq中包含两大功能块:PS部分和PL部分。

上一节我们体验了一把PS和PL是怎样联合开发的,这种ARM和FPGA联合设计是ZYNQ的精华所在。这一节我们实现一个稍微复杂一点的功能——测量未知信号的频率,PS和PL通过AXI总线交互数据,实现我们希望的功能。

如何测量数字信号的频率

最简单的办法——在一段时间内计数

在我们设定的时间(Tpr) 内对被测信号的脉冲进行计数, 得Nx, Fx=Nx/Tpr。

Tpr 越大,测频精度越高。这种方法适合于高频信号,因为这里可能会有一个被测信号周期的误差,测量高频信号时误差小。

另一个变种——在一个周期内计数

在 被测信号一个周期内对基准时钟信号计数,得Nx, 基准时钟周期为T, 则Tx=T*Nx, Fx=1/Tx。

被测信号频率越低, 基准时钟频率越高,测量精度越高。因此这种方法适用于低频信号。

二者结合——多个周期同步计数

上一篇中提到了SLICEL和SLICEM都可用作ROM,后者还可以作为分布式RAM(Distribute RAM,DRAM)。本篇主要总结的是块状Memory(Block Memory),实际上就是FPGA内部独立于逻辑单元的专用存储器,更像是一种硬核。

1. 基本结构

如下图所示,一个Block Memory的大小为36KB(RAMB36E1),由两个独立的18KB BRAM(Block RAM,RAMB18E1)组成。因此一个36K的Block Memory可配置成4中情形:

为什么不能配置成两个18KB的FIFO呢?因为一个Block Momery中间有一个叫FIFO Logic的结构,它用于生成FIFO控制信号,包括读/写地址等,由于它只有1个且不能共享,所以最多只能配置一个FIFO。

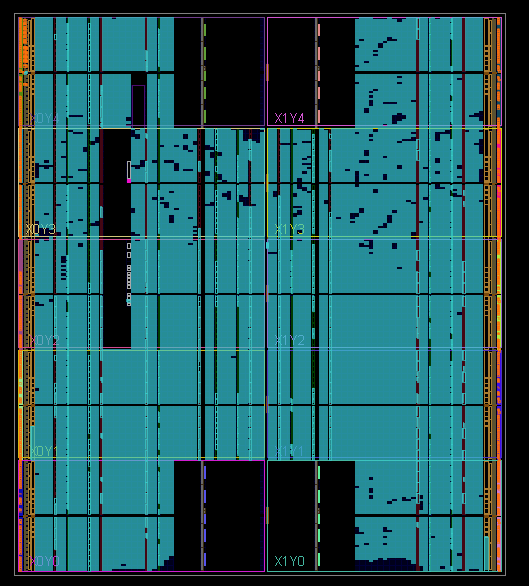

一直以来,觉得自己关于FPGA方面,摸不到“低”——对底层架构认识不清,够不着“高”——没真正独立做过NB的应用,如高速、复杂协议或算法、神经网络加速等高大上的应用,所以能力和认识水平都处于中间水平。这段时间做时序优化,感觉心有余而力不足了,可能要触及手动布局布线了,打开Device布局图才开始有兴趣探究一些底层结构的东西。

看吧,资源已经用了80%的A7 200芯片

可能翻开任何一本有关FPGA的书籍,上来就会介绍FPGA的历史,原理,内部结构什么的,大部分人看着都极其枯燥,常常要么直接略过,要么就看一遍,久了也就忘记了(部分靠翻译文档的书作者该好好反思)。我硬着头皮去弥补之前缺失的一些基础知识,结合Xilinx A7 芯片,总结一下自己的收获。