System Generator从入门到放弃(八)-使用多时钟域实现多速率系统设计

judy 在 周五, 02/15/2019 - 09:13 提交

多速率的概念是相对于单速率(Single Rate)信号处理而言的。单速率是指整个信号处理流程中只有一种数据速率;多速率是指系统中存在多个数据速率。使用多速率信号处理可以节省存储空间、减少通信数据量、减少运算量、减轻设计难度

多速率的概念是相对于单速率(Single Rate)信号处理而言的。单速率是指整个信号处理流程中只有一种数据速率;多速率是指系统中存在多个数据速率。使用多速率信号处理可以节省存储空间、减少通信数据量、减少运算量、减轻设计难度

ZynqNet能在xilinx的FPGA上实现deep compression的网络。目的:读懂ZynqNetCPU端的代码。

Vivado综合工具支持直接在RTL文件或XDC文件中设置综合属性。如果Vivado识别出设置的属性,会创建与之相关的逻辑电路;如果不能识别设置的属性,会将该属性和值存放在生成的网表中。因为某些属性,比如LOC约束适用于布线过程,因此必须保留该属性配置情况

背景:ZynqNet能在xilinx的FPGA上实现deep compression

目的:运行zynqNet的代码。

源码地址:https://github.com/dgschwend/zynqnet

项目程序架构,针对我们的项目,我们需要看懂相应的HLS程序和ARM端的程序。

ARM端的程序以_FIRMWARE为准;FPGA端程序以HLS为准。

1. _TRAINED_MODEL

这部分为训练好的caffe模型与预训练的权重。

2. _FIRMWARE

这部分程序针对Zynq 7Z035 ARM processor。make之后是在服务器上运行的,一次迭代需要将近3590ms

make

./test CPU|FPGA indata.bin (-quiet)

本文是我在学习FPGA时学到的相关知识与总结,希望可以帮助同行理解和掌握相关的FPGA知识。可以将本文档当作相应FPGA教程文档UG998的辅助文档学习。

Xilinx原版教程文档参见XilinxDocumentation navigator 中对应UG998:Introduction to FPGA Design with Vivado High-Level Synthesis

0.简介:

UG998文档主要介绍一些基础的关于FPGA和硬件设计相关的知识,例如什么是FPGA,硬件设计的基本概念,vivado软件的高层综合,以运算为中心的算法(Computation-Centric Algorithms),以控制为中心的算法(Control-CentricAlgorithms),软件验证和vivado HLS软件,多程序集成,应用的验证。用于初学者有一个初步的理念。

Chapter 1

首先要说明的是,往zedboard上移植opencv跟我们平时在pc上安装opencv的过程不同。毕竟zedboard是嵌入式平台很多东西都要删减,而且zedboard官方移植的linux不带图形界面,我们要自己在命令行下配置环境

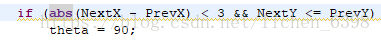

在viado SDK的程序开发中会出现以下的问题

出现问题的原因可能是

没有添加对应的头文件

解决办法:添加对应的头文件 如上图:添加#include”stdlib.h”

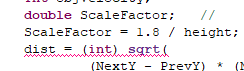

没有添加库函数

解决的方法是:

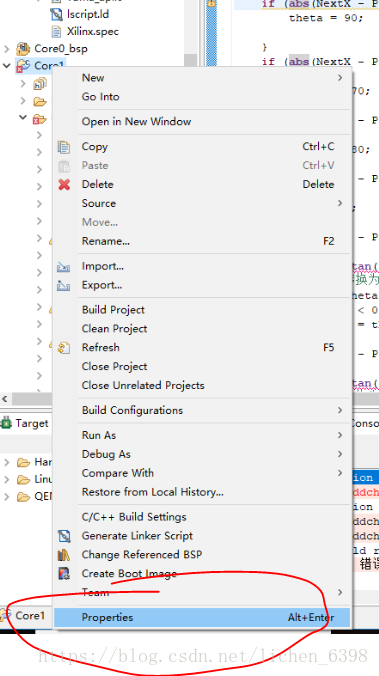

点击工程文件,右键,选择Properties

如下图:

选择 C/C++ Build 下的Setting 选择:Libraries 添加m文件 因为abs()位于math.h函数里

背景:ZynqNet能在xilinx的FPGA上实现deep compression。

目的:读懂zynqNet的代码和论文。

一、网络所需的运算与存储

1.1 运算操作:

1.2 Memory requirements:

1.3 需求分析:

在介绍Gateway In block时谈到了System Generator中的数据类型,及不同的量化和溢出方式。本文将以两个简单的设计实例,更直观地说明不同的量化和溢出方式有什么区别。

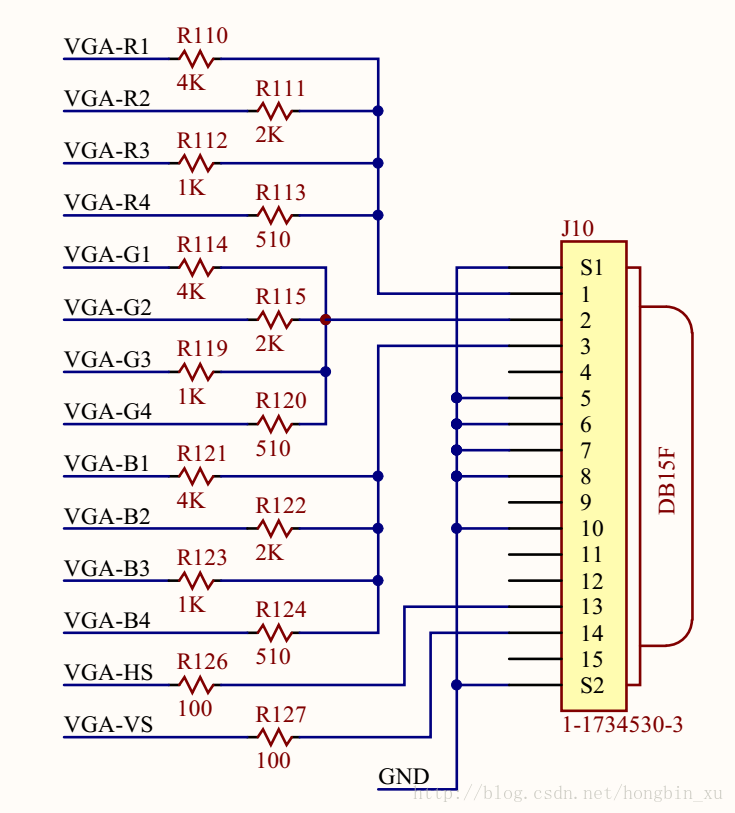

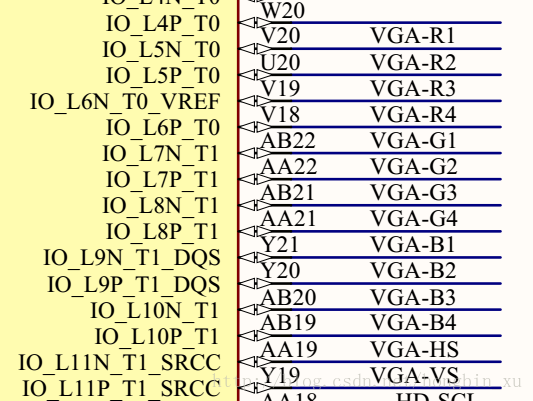

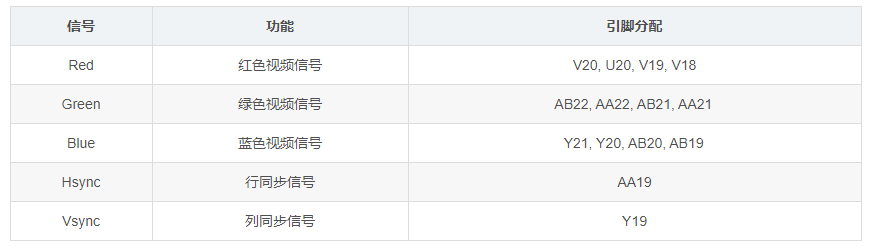

VGA硬件接口

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

上面给出了所有的引脚分配。

VGA时序分析