Zedboard学习(六):XADC读取数据

judy 在 周四, 01/24/2019 - 11:12 提交

zynq 的内嵌了 XADC,可以用来采集电压;

Temp:芯片温度

VCCINT: 内部PL核心电压

VCCAUX: 辅助PL电压

VCCBram: PL BRAM电压

VCCPInt: PS内部核心电压

VCCPAux: PS辅助电压

VCCDDR: DDR RAM的工作电压

VREFP: XADC正参考电压

VREFN: XADC负参考电压

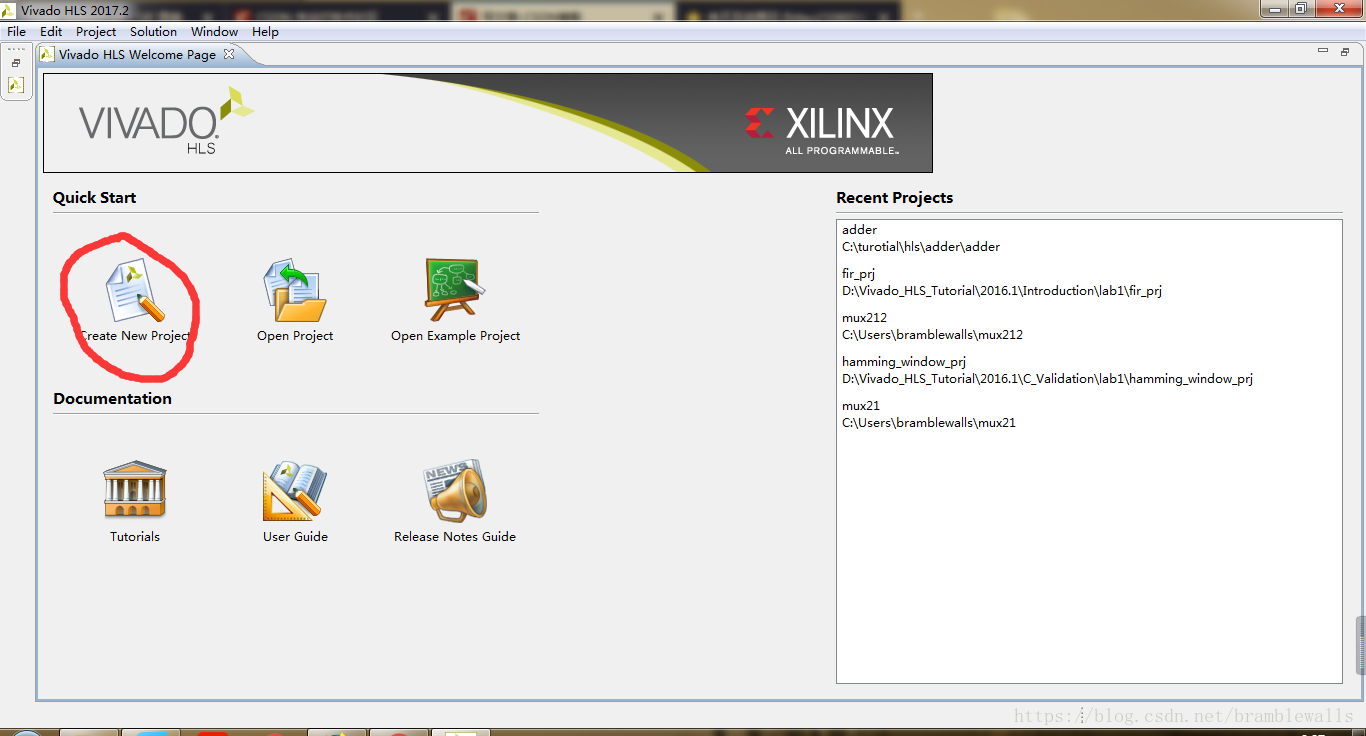

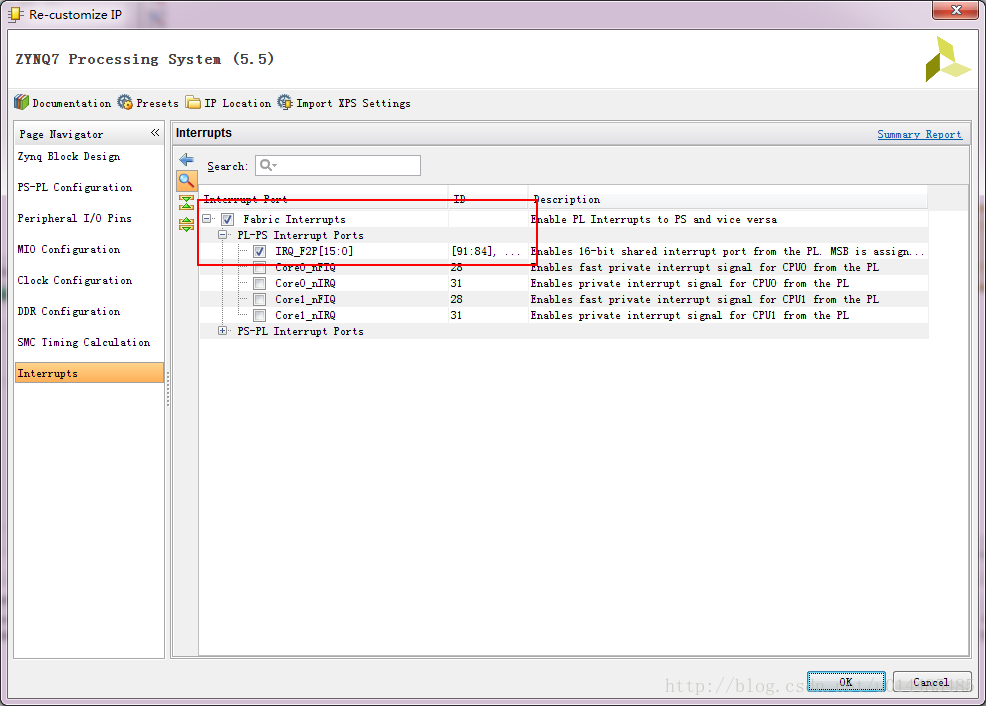

1、新建工程,添加block design。添加zynq7 processor和xadc模块。

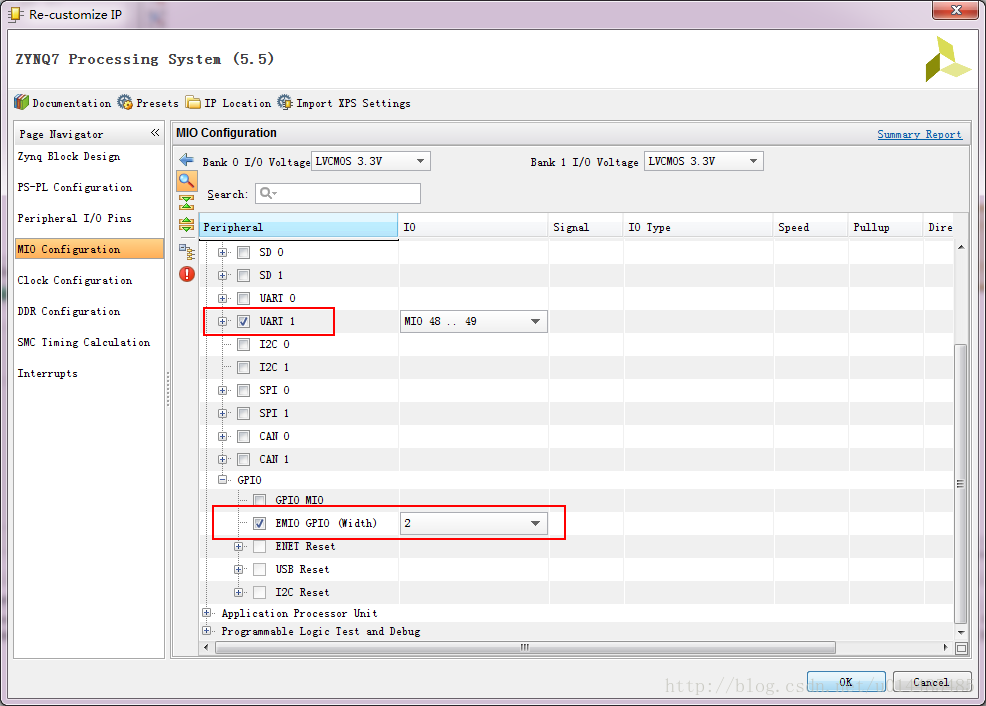

2、Run Block Automation后会自动配置zynq7处理器;Run Connection Automation 会自动将模块进行连接,将xadc模块挂载在axi总线下,这样xadc的相关寄存器会映射到处理器的内存(DDR)上。自动添加的两个模块,一个用于管理全局复位,一个用于同步axi总线。